# UM0404 User manual

# High performance ST10F276Z5 and ST10F276E 16-bit microcontrollers

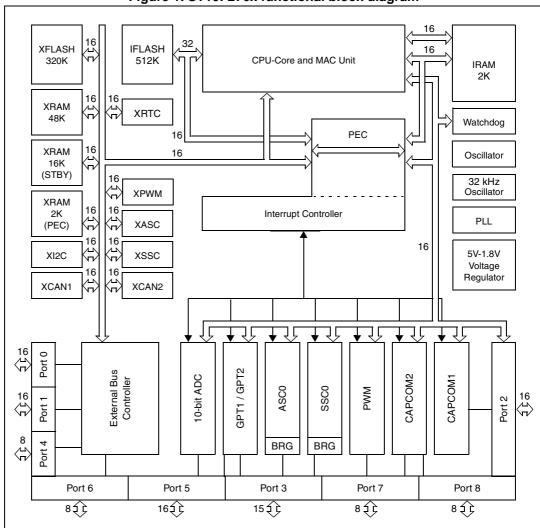

#### Introduction

This manual describes the functionality of the ST10F276Z5 and ST10F276E devices.

An architectural overview describes the CPU performance, the on-chip system resources, the on-chip clock generator, the on-chip peripheral blocks and the protected bits.

The operation of the CPU and the on-chip peripherals, and the different operating modes - such as system reset, power reduction modes, interrupt handling, and system programming - are described in individual sections.

The explanation of memory configuration has been restricted to that of the internal addressable memory space. The ST10F276Z5 and ST10F276E Flash configurations are not discussed in this manual. Refer to the ST10F276Z5 and ST10F276E datasheets for detailed information (see *Appendix B: Document references*).

The Special Functional Registers are listed both by name and hexadecimal address. The instruction set is covered in full in the *ST10 Family Programming Manual* and is, therefore, not discussed in this manual. However, software programming feature - including constructs for modularity, loops, and context switching - are described in *Section 27: System programming on page 525*.

The DC and AC electrical specifications of the device and the pin description for each available package, are not covered in this manual but are listed in the specific device datasheets.

Before starting on a new design, verify the device characteristics and pinout with an up-todate copy of the device datasheet.

The ST10F276Z5 and ST10F276E software and hardware development tools include:

- Compilers (C, C++), macro-assemblers, linkers, locators, library managers, formatconverters from Tasking & Keil

- HLL debuggers

- · Real-time operating systems

- In-circuit emulators (based on Bond-out ST chips) from Hitex, Lauterbach, Nohau

- Logic analyzer disassemblers

- Evaluation boards with monitor programs from FORTH

- Industrial embedded Flash programming software from PLS

- Network driver software (CAN)

May 2013 DocID13284 Rev 2 1/564

Contents UM0404

# **Contents**

| 1 | Arch | nitectura | l overview                                        | . 22 |

|---|------|-----------|---------------------------------------------------|------|

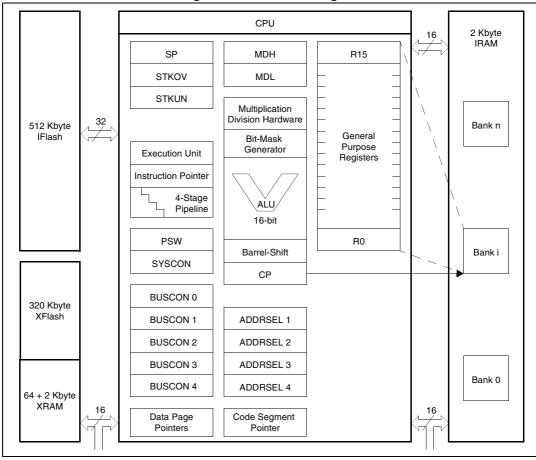

|   | 1.1  | Basic C   | CPU concepts and optimization                     | . 22 |

|   |      | 1.1.1     | High instruction bandwidth / fast execution       | 24   |

|   |      | 1.1.2     | High function 8-bit and 16-bit ALU                | 25   |

|   |      | 1.1.3     | Extended bit processing and peripheral control    | 25   |

|   |      | 1.1.4     | High performance branch, call and loop processing | 25   |

|   |      | 1.1.5     | Consistent and optimized instruction formats      | 26   |

|   |      | 1.1.6     | Programmable multiple priority interrupt system   | 27   |

|   | 1.2  | On-chip   | system resources                                  | . 27 |

|   |      | 1.2.1     | Peripheral event control and interrupt control    | 28   |

|   |      | 1.2.2     | Memory areas                                      | 28   |

|   |      | 1.2.3     | External bus interface                            | 29   |

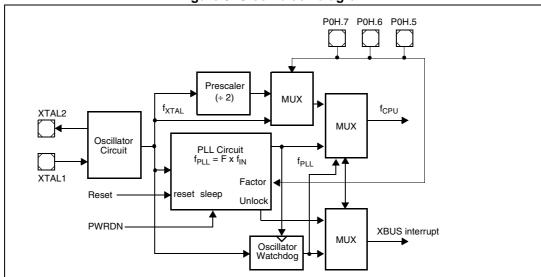

|   | 1.3  | Clock g   | generator                                         | . 30 |

|   |      | 1.3.1     | PLL operation                                     | 31   |

|   |      | 1.3.2     | Prescaler operation                               | 31   |

|   |      | 1.3.3     | Direct drive                                      | 31   |

|   |      | 1.3.4     | Oscillator watchdog (OWD)                         | 32   |

|   | 1.4  | On-chip   | peripheral blocks                                 | . 32 |

|   |      | 1.4.1     | Peripheral interfaces                             | 33   |

|   |      | 1.4.2     | Peripheral timing                                 | 33   |

|   |      | 1.4.3     | Programming hints                                 | 33   |

|   |      | 1.4.4     | Parallel ports                                    | 34   |

|   |      | 1.4.5     | Serial channels                                   | 34   |

|   |      | 1.4.6     | General purpose timer (GPT) unit                  | 35   |

|   |      | 1.4.7     | Watchdog timer                                    | 36   |

|   |      | 1.4.8     | Capture / compare (CAPCOM) units                  | 36   |

|   |      | 1.4.9     | Pulse width modulation unit                       | 37   |

|   |      | 1.4.10    | A/D converter                                     | 37   |

|   |      | 1.4.11    | CAN module                                        | 38   |

|   |      | 1.4.12    | I2C serial interface                              | 38   |

|   | 1.5  | Real tir  | ne clock                                          | . 38 |

|   | 1.6  | Protect   | ed bits                                           | . 39 |

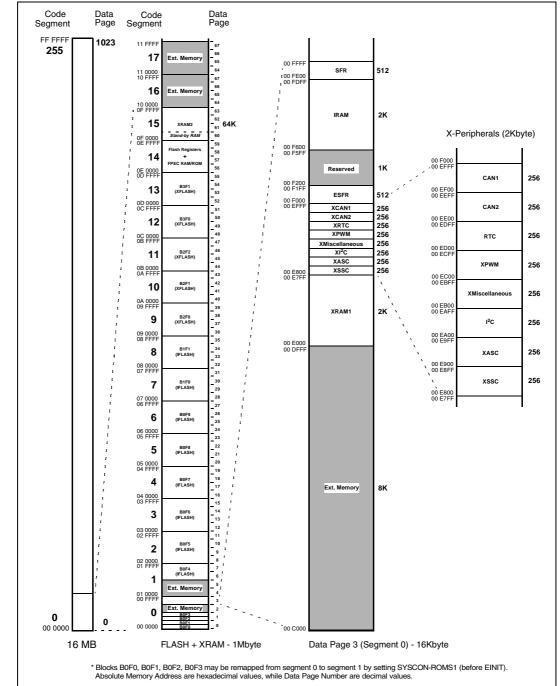

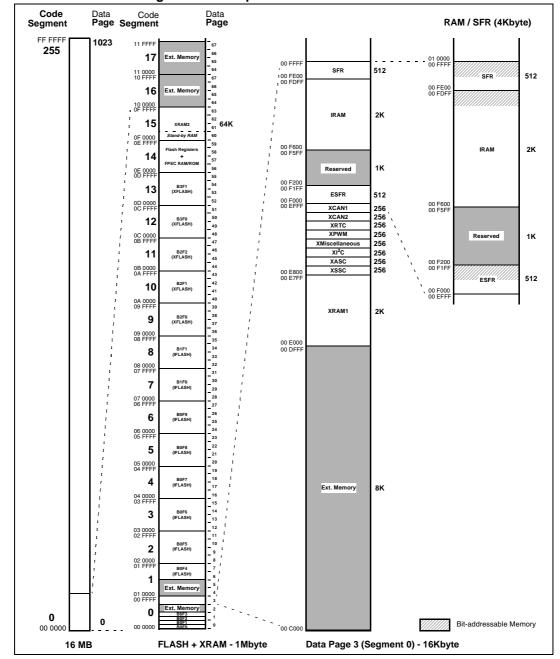

| 2 | Mem  | nory org  | anization                                         | . 40 |

|   |      |           |                                                   |      |

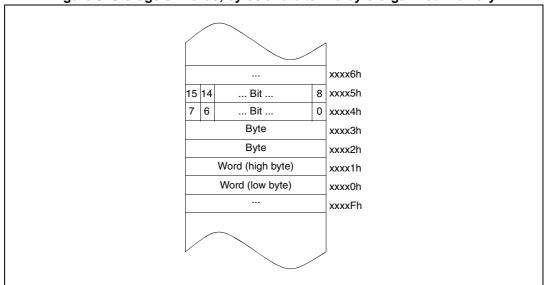

|   | 2.1   | Word, b   | yte and bit storage                           | 41   |

|---|-------|-----------|-----------------------------------------------|------|

|   | 2.2   | On-chip   | Flash                                         | 42   |

|   | 2.3   | IRAM a    | nd SFR area                                   | 44   |

|   |       | 2.3.1     | System stack                                  | . 46 |

|   |       | 2.3.2     | General purpose registers                     | . 46 |

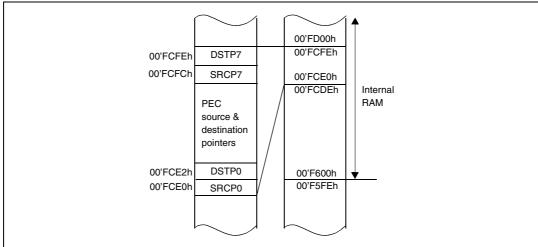

|   |       | 2.3.3     | PEC source and destination pointers           | . 47 |

|   |       | 2.3.4     | Special function registers                    | . 48 |

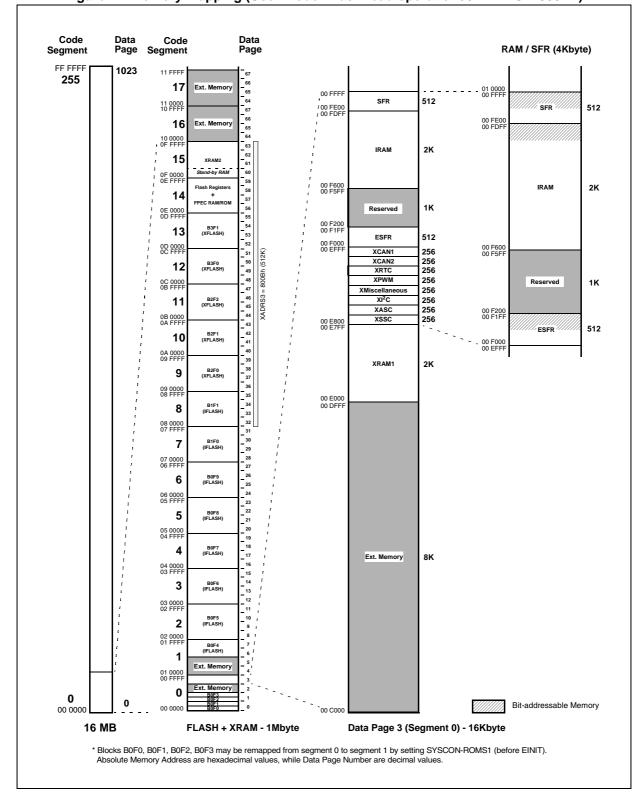

|   | 2.4   | The on-   | chip XRAM                                     | 49   |

|   |       | 2.4.1     | XRAM access via external masters              | . 50 |

|   | 2.5   | Externa   | I memory space                                | 50   |

|   | 2.6   | Crossin   | g memory boundaries                           | 51   |

| 3 | The c | entral p  | processing unit (CPU)                         | 52   |

|   | 3.1   |           | on pipelines                                  |      |

|   | 0.1   | 3.1.1     | Sequential instruction processing             |      |

|   |       | 3.1.2     | Standard branch instruction processing        |      |

|   |       | 3.1.3     | Cache jump instruction processing             |      |

|   |       | 3.1.4     | Particular pipeline effects                   |      |

|   | 3.2   | Bit-hand  | dling and bit-protection                      | 59   |

|   | 3.3   | Instructi | on execution times                            | 60   |

|   | 3.4   | CPU sp    | ecial function registers                      | 61   |

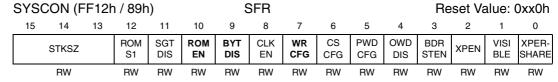

|   |       | 3.4.1     | The system configuration register SYSCON      | . 62 |

|   |       | 3.4.2     | X-Peripherals control register (XPERCON)      | . 65 |

|   |       | 3.4.3     | XPERCON and XPEREMU registers                 | . 66 |

|   |       | 3.4.4     | Emulation dedicated registers                 | . 67 |

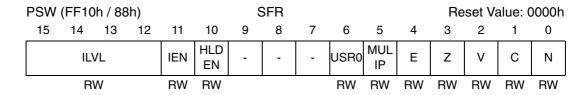

|   |       | 3.4.5     | The processor status word PSW                 | . 67 |

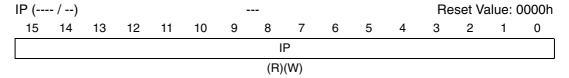

|   |       | 3.4.6     | The instruction pointer IP                    | . 70 |

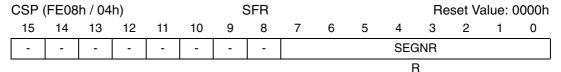

|   |       | 3.4.7     | The code segment pointer CSP                  | . 71 |

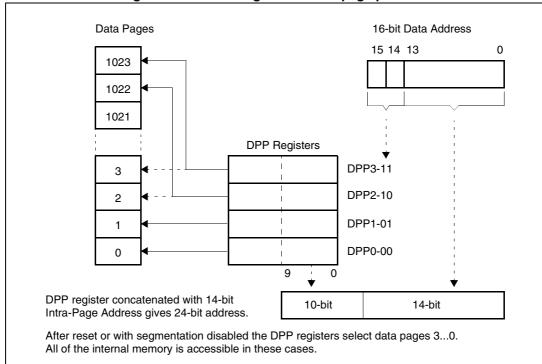

|   |       | 3.4.8     | The data page pointers DPP0, DPP1, DPP2, DPP3 | . 72 |

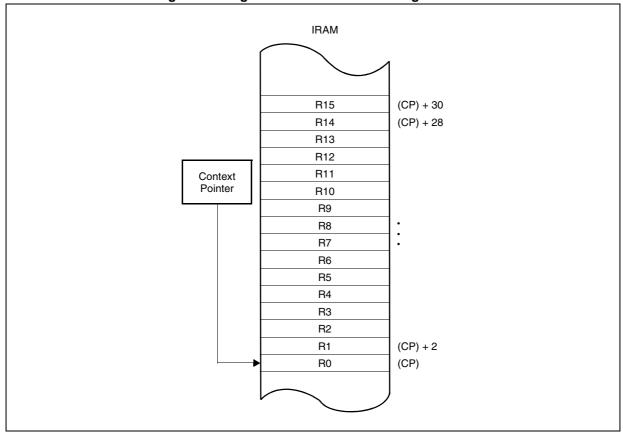

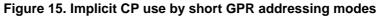

|   |       | 3.4.9     | The context pointer CP                        | . 73 |

|   |       | 3.4.10    | The stack pointer SP                          | . 76 |

|   |       | 3.4.11    | The stack overflow pointer STKOV              | . 76 |

|   |       | 3.4.12    | The stack underflow pointer STKUN             | . 77 |

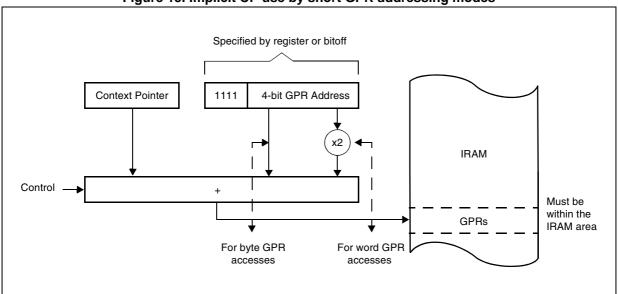

|   |       | 3.4.13    | The multiply / divide high register MDH       |      |

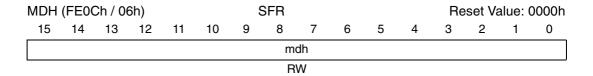

|   |       | 3.4.14    | The multiply / divide low register MDL        |      |

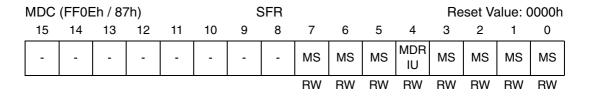

|   |       | 3.4.15    | The multiply / divide control register MDC    | . 79 |

|   |       |           |                                               |      |

|   |        | 3.4.16    | The constant zeros register ZEROS             | 79    |

|---|--------|-----------|-----------------------------------------------|-------|

|   |        | 3.4.17    | The constant ones register ONES               | 81    |

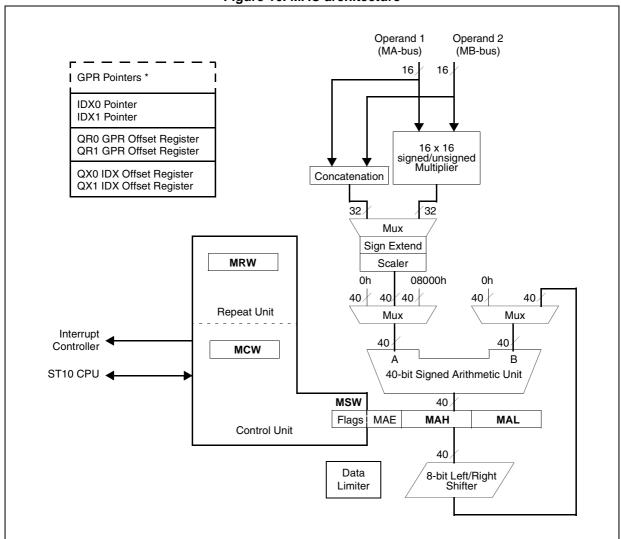

| 4 | Multi  | ply-acc   | umulate unit (MAC)                            | 82    |

|   | 4.1    | MAC fe    | eatures                                       | 82    |

|   | 4.2    | MAC o     | peration                                      | 83    |

|   |        | 4.2.1     | Instruction pipelining                        | 84    |

|   |        | 4.2.2     | Particular pipeline effects with the MAC unit | 84    |

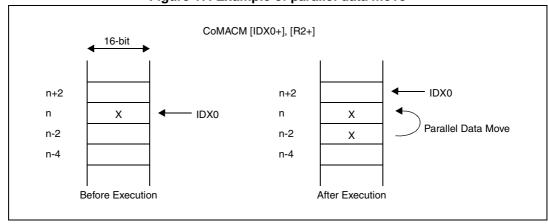

|   |        | 4.2.3     | Address generation                            | 85    |

|   |        | 4.2.4     | 16 x 16 signed/unsigned parallel multiplier   | 86    |

|   |        | 4.2.5     | 40-bit signed arithmetic unit                 | 86    |

|   |        | 4.2.6     | The 40-bit signed accumulator register        | 87    |

|   |        | 4.2.7     | The 40-bit adder / subtracter                 | 88    |

|   |        | 4.2.8     | Data limiter                                  | 88    |

|   |        | 4.2.9     | The accumulator shifter                       | 89    |

|   |        | 4.2.10    | Repeat unit                                   | 89    |

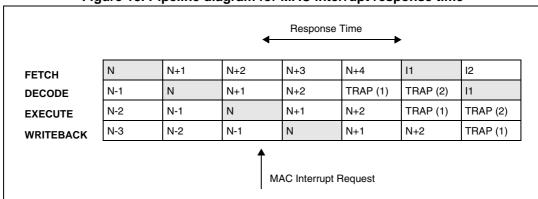

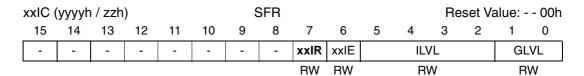

|   |        | 4.2.11    | MAC interrupt                                 | 90    |

|   |        | 4.2.12    | Number representation & rounding              | 90    |

|   | 4.3    | MAC re    | egister set                                   | 91    |

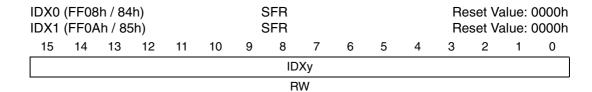

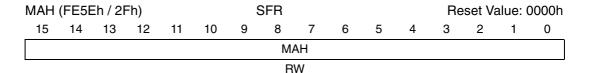

|   |        | 4.3.1     | Address registers                             | 91    |

|   |        | 4.3.2     | Accumulator & control registers               | 91    |

|   | 4.4    | MAC in    | struction set summary                         | 94    |

| 5 | Interr | rupt and  | d trap functions                              | 96    |

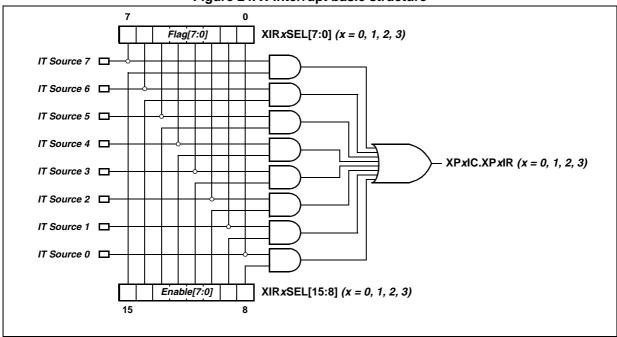

|   | 5.1    | Interrup  | ot system structure                           | 96    |

|   |        | 5.1.1     | Normal interrupt processing and PEC service   | 100   |

|   |        | 5.1.2     | Interrupt system register description         | 100   |

|   |        | 5.1.3     | Interrupt control registers                   | 100   |

|   |        | 5.1.4     | Interrupt priority level and group level      | 101   |

|   |        | 5.1.5     | Interrupt control functions in the PSW        | 103   |

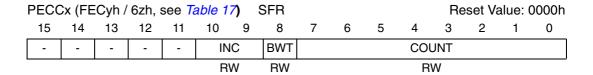

|   | 5.2    | Operati   | on of the PEC channels                        | . 104 |

|   | 5.3    | Prioritiz | ring interrupt & PEC service requests         | . 106 |

|   |        | 5.3.1     | Enabling and disabling interrupt requests     | 106   |

|   |        | 5.3.2     | Interrupt class management                    | 107   |

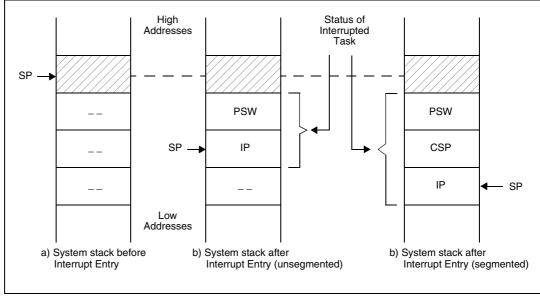

|   | 5.4    | Saving    | the status during interrupt service           |       |

|   |        | 5.4.1     | Context switching                             |       |

|   |        |           |                                               |       |

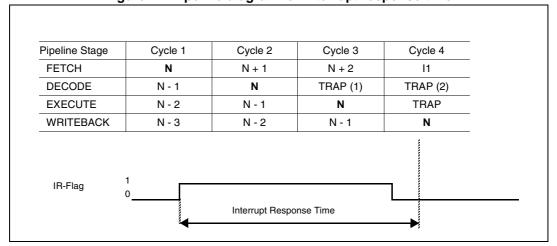

|   | 5.5                                                                   | Interrup                                                                                                                         | ot response times                                                                                                                                                                                                                                                                 | 110                                                                                            |

|---|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|   |                                                                       | 5.5.1                                                                                                                            | PEC response times                                                                                                                                                                                                                                                                | 111                                                                                            |

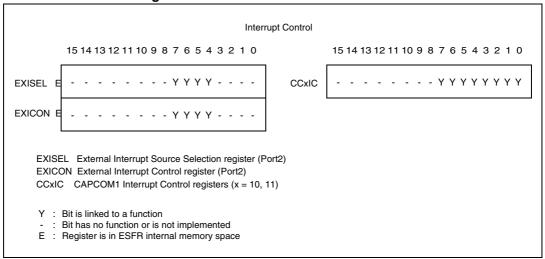

|   | 5.6                                                                   | Externa                                                                                                                          | al interrupts                                                                                                                                                                                                                                                                     | 113                                                                                            |

|   |                                                                       | 5.6.1                                                                                                                            | Fast external interrupts                                                                                                                                                                                                                                                          | 115                                                                                            |

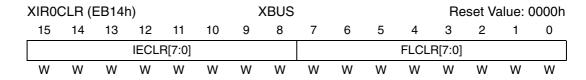

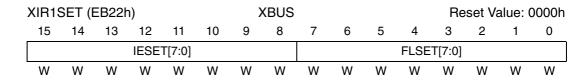

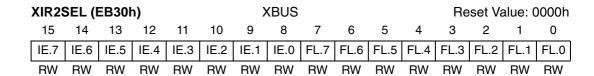

|   | 5.7                                                                   | X-perip                                                                                                                          | heral interrupt                                                                                                                                                                                                                                                                   | 117                                                                                            |

|   | 5.8                                                                   | Trap fu                                                                                                                          | nctions                                                                                                                                                                                                                                                                           | . 128                                                                                          |

|   |                                                                       | 5.8.1                                                                                                                            | Software traps                                                                                                                                                                                                                                                                    | 129                                                                                            |

|   |                                                                       | 5.8.2                                                                                                                            | Hardware traps                                                                                                                                                                                                                                                                    | 129                                                                                            |

|   |                                                                       | 5.8.3                                                                                                                            | External NMI trap                                                                                                                                                                                                                                                                 | 131                                                                                            |

|   |                                                                       | 5.8.4                                                                                                                            | Stack overflow trap                                                                                                                                                                                                                                                               | 131                                                                                            |

|   |                                                                       | 5.8.5                                                                                                                            | Stack underflow trap                                                                                                                                                                                                                                                              | 132                                                                                            |

|   |                                                                       | 5.8.6                                                                                                                            | Undefined opcode trap                                                                                                                                                                                                                                                             | 132                                                                                            |

|   |                                                                       | 5.8.7                                                                                                                            | MAC interrupt                                                                                                                                                                                                                                                                     | 132                                                                                            |

|   |                                                                       | 5.8.8                                                                                                                            | Protection fault trap                                                                                                                                                                                                                                                             | 132                                                                                            |

|   |                                                                       | 5.8.9                                                                                                                            | Illegal word operand access trap                                                                                                                                                                                                                                                  | 133                                                                                            |

|   |                                                                       | 5.8.10                                                                                                                           | Illegal instruction access trap                                                                                                                                                                                                                                                   | 133                                                                                            |

|   |                                                                       | 5.8.11                                                                                                                           | Illegal external bus access trap                                                                                                                                                                                                                                                  | 133                                                                                            |

| 6 | Para                                                                  | llel nort                                                                                                                        | S                                                                                                                                                                                                                                                                                 | 13/                                                                                            |

| U | i aia                                                                 | mer port                                                                                                                         | 3                                                                                                                                                                                                                                                                                 | . 137                                                                                          |

|   | 6 1                                                                   | Introdu                                                                                                                          | ation                                                                                                                                                                                                                                                                             | 101                                                                                            |

|   | 6.1                                                                   |                                                                                                                                  | Chan drain made                                                                                                                                                                                                                                                                   |                                                                                                |

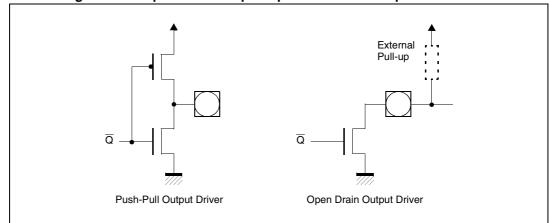

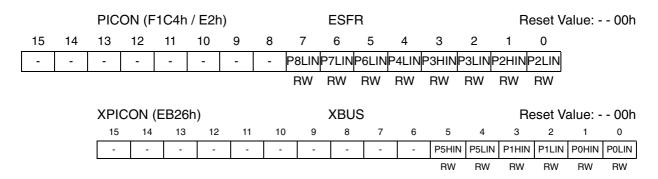

|   | 6.1                                                                   | 6.1.1                                                                                                                            | Open drain mode                                                                                                                                                                                                                                                                   | 134                                                                                            |

|   | 6.1                                                                   | 6.1.1<br>6.1.2                                                                                                                   | Open drain mode                                                                                                                                                                                                                                                                   | 134                                                                                            |

|   |                                                                       | 6.1.1<br>6.1.2<br>6.1.3                                                                                                          | Open drain mode                                                                                                                                                                                                                                                                   | 134<br>137<br>138                                                                              |

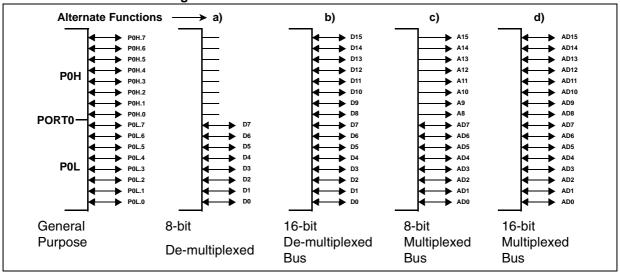

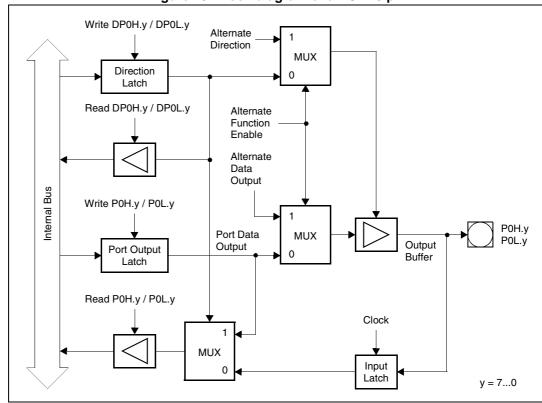

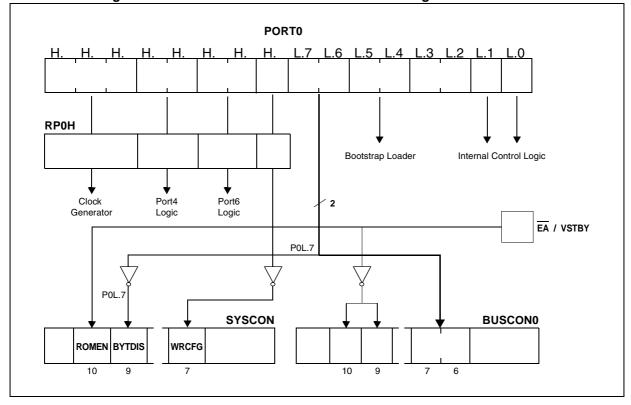

|   | 6.1                                                                   | 6.1.1<br>6.1.2<br>6.1.3<br>PORT0                                                                                                 | Open drain mode                                                                                                                                                                                                                                                                   | 134<br>137<br>138<br>139                                                                       |

|   | 6.2                                                                   | 6.1.1<br>6.1.2<br>6.1.3<br>PORT0<br>6.2.1                                                                                        | Open drain mode                                                                                                                                                                                                                                                                   | 134<br>137<br>138<br>. 139<br>140                                                              |

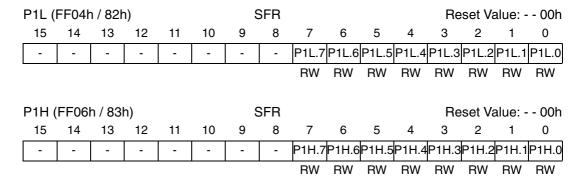

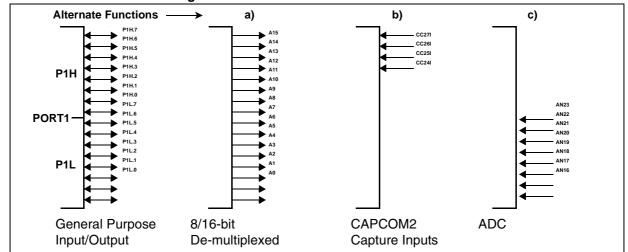

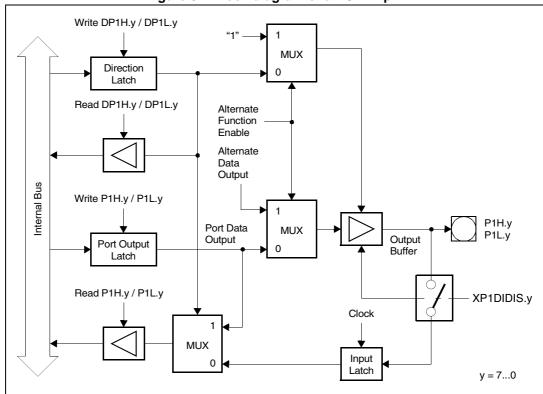

|   |                                                                       | 6.1.1<br>6.1.2<br>6.1.3<br>PORT0<br>6.2.1<br>PORT1                                                                               | Open drain mode                                                                                                                                                                                                                                                                   | 134<br>137<br>138<br>139<br>140<br>142                                                         |

|   | 6.2                                                                   | 6.1.1<br>6.1.2<br>6.1.3<br>PORT0<br>6.2.1<br>PORT1<br>6.3.1                                                                      | Open drain mode Input threshold control Alternate port functions  Alternate functions of PORT0  Alternate functions of PORT1                                                                                                                                                      | 134<br>137<br>138<br>139<br>140<br>142<br>143                                                  |

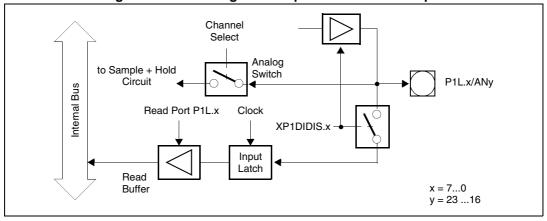

|   | 6.2<br>6.3                                                            | 6.1.1<br>6.1.2<br>6.1.3<br>PORT0<br>6.2.1<br>PORT1<br>6.3.1<br>6.3.2                                                             | Open drain mode Input threshold control Alternate port functions  Alternate functions of PORT0  Alternate functions of PORT1  PORT1 analog inputs disturb protection                                                                                                              | 134<br>137<br>138<br>139<br>140<br>142<br>143<br>144                                           |

|   | 6.2                                                                   | 6.1.1<br>6.1.2<br>6.1.3<br>PORTO<br>6.2.1<br>PORT1<br>6.3.1<br>6.3.2<br>Port2 .                                                  | Open drain mode Input threshold control Alternate port functions  Alternate functions of PORT0  Alternate functions of PORT1  PORT1 analog inputs disturb protection                                                                                                              | 134<br>137<br>138<br>140<br>142<br>143<br>144                                                  |

|   | 6.2<br>6.3                                                            | 6.1.1<br>6.1.2<br>6.1.3<br>PORTO<br>6.2.1<br>PORT1<br>6.3.1<br>6.3.2<br>Port2 .                                                  | Open drain mode Input threshold control Alternate port functions  Alternate functions of PORT0  Alternate functions of PORT1  PORT1 analog inputs disturb protection  Alternate functions of Port2                                                                                | 134<br>137<br>138<br>140<br>142<br>143<br>144<br>146<br>147                                    |

|   | 6.2<br>6.3<br>6.4                                                     | 6.1.1<br>6.1.2<br>6.1.3<br>PORTO<br>6.2.1<br>PORT1<br>6.3.1<br>6.3.2<br>Port2 .<br>6.4.1<br>6.4.2                                | Open drain mode Input threshold control Alternate port functions  Alternate functions of PORT0  Alternate functions of PORT1  PORT1 analog inputs disturb protection  Alternate functions of Port2  External interrupts                                                           | 134<br>137<br>138<br>140<br>142<br>143<br>144<br>146<br>147<br>148                             |

|   | 6.2<br>6.3                                                            | 6.1.1<br>6.1.2<br>6.1.3<br>PORTO<br>6.2.1<br>PORT1<br>6.3.1<br>6.3.2<br>Port2 .<br>6.4.1<br>6.4.2<br>Port3 .                     | Open drain mode Input threshold control Alternate port functions  Alternate functions of PORT0  Alternate functions of PORT1  PORT1 analog inputs disturb protection  Alternate functions of Port2  External interrupts                                                           | 134<br>137<br>138<br>140<br>142<br>143<br>144<br>146<br>147<br>148<br>150                      |

|   | 6.2<br>6.3<br>6.4                                                     | 6.1.1<br>6.1.2<br>6.1.3<br>PORTO<br>6.2.1<br>PORT1<br>6.3.1<br>6.3.2<br>Port2 .<br>6.4.1<br>6.4.2<br>Port3 .                     | Open drain mode Input threshold control Alternate port functions  Alternate functions of PORT0  Alternate functions of PORT1 PORT1 analog inputs disturb protection  Alternate functions of Port2 External interrupts  Alternate functions of Port3                               | 134<br>137<br>138<br>. 139<br>140<br>142<br>143<br>144<br>146<br>147<br>148<br>150             |

|   | 6.2<br>6.3<br>6.4                                                     | 6.1.1<br>6.1.2<br>6.1.3<br>PORTO<br>6.2.1<br>PORT1<br>6.3.1<br>6.3.2<br>Port2 .<br>6.4.1<br>6.4.2<br>Port3 .<br>6.5.1<br>Port4 . | Open drain mode Input threshold control Alternate port functions  Alternate functions of PORT0  Alternate functions of PORT1 PORT1 analog inputs disturb protection  Alternate functions of Port2 External interrupts  Alternate functions of Port3                               | 134<br>137<br>138<br>. 139<br>140<br>142<br>143<br>144<br>146<br>147<br>148<br>150<br>151      |

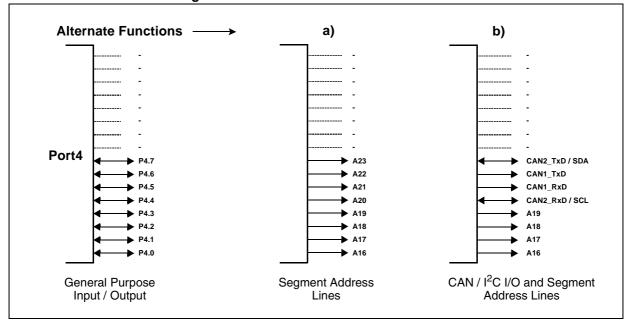

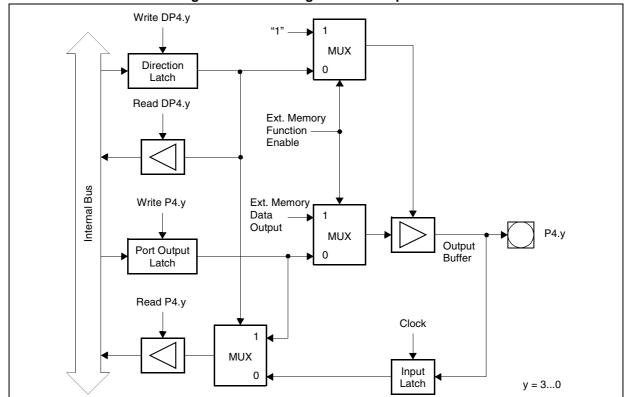

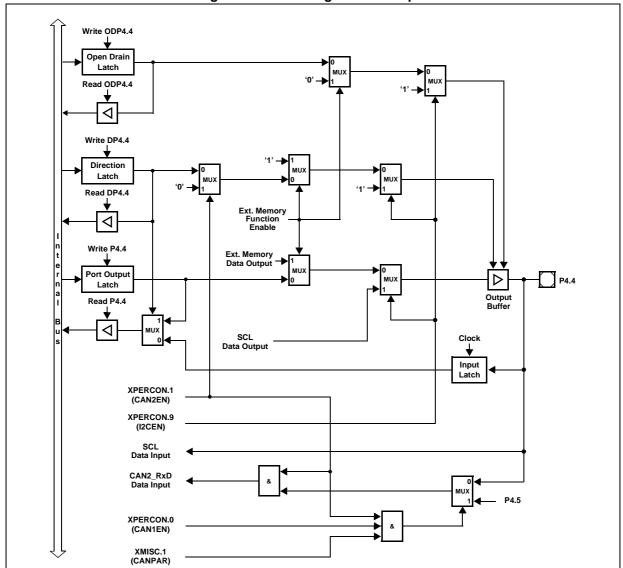

|   | <ul><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li><li>6.6</li></ul> | 6.1.1<br>6.1.2<br>6.1.3<br>PORTO<br>6.2.1<br>PORT1<br>6.3.1<br>6.3.2<br>Port2 .<br>6.4.1<br>6.4.2<br>Port3 .<br>6.5.1<br>Port4 . | Open drain mode Input threshold control Alternate port functions  Alternate functions of PORT0  Alternate functions of PORT1 PORT1 analog inputs disturb protection  Alternate functions of Port2 External interrupts  Alternate functions of Port3  Alternate functions of Port4 | 134<br>137<br>138<br>139<br>140<br>143<br>144<br>146<br>147<br>148<br>150<br>151<br>154<br>155 |

|   | 6.2<br>6.3<br>6.4                                                     | 6.1.1<br>6.1.2<br>6.1.3<br>PORTO<br>6.2.1<br>PORT1<br>6.3.1<br>6.3.2<br>Port2 .<br>6.4.1<br>6.4.2<br>Port3 .<br>6.5.1<br>Port4 . | Open drain mode Input threshold control Alternate port functions  Alternate functions of PORT0  Alternate functions of PORT1 PORT1 analog inputs disturb protection  Alternate functions of Port2 External interrupts  Alternate functions of Port3                               | 134<br>137<br>138<br>139<br>140<br>143<br>144<br>146<br>147<br>148<br>150<br>151<br>154<br>155 |

|   |                            | 6.7.1    | Alternate functions of Port5                  | 162 |  |  |

|---|----------------------------|----------|-----------------------------------------------|-----|--|--|

|   |                            | 6.7.2    | Port5 analog inputs disturb protection        |     |  |  |

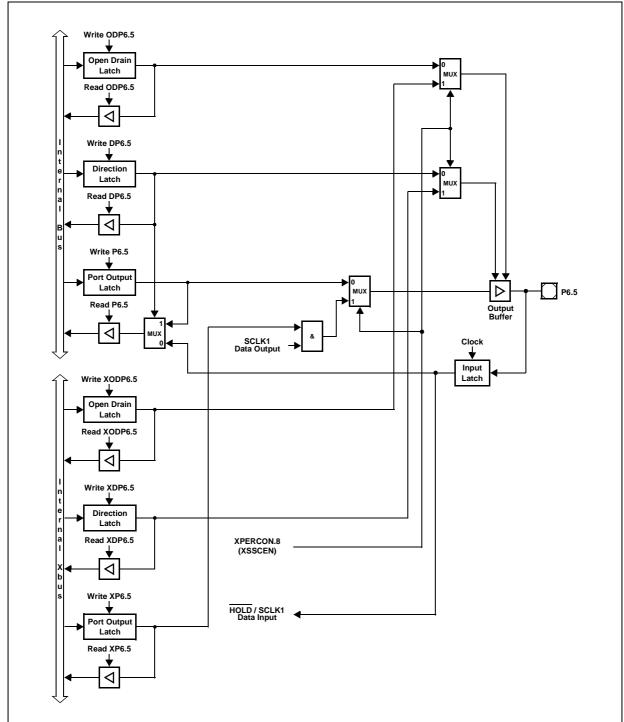

|   | 6.8                        |          |                                               |     |  |  |

|   | 0.0                        | 6.8.1    | Alternate functions of Port6                  |     |  |  |

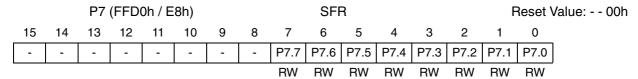

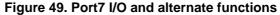

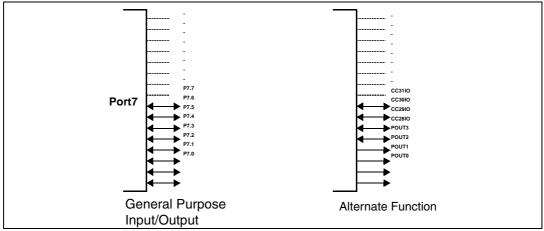

|   | 6.9                        |          |                                               |     |  |  |

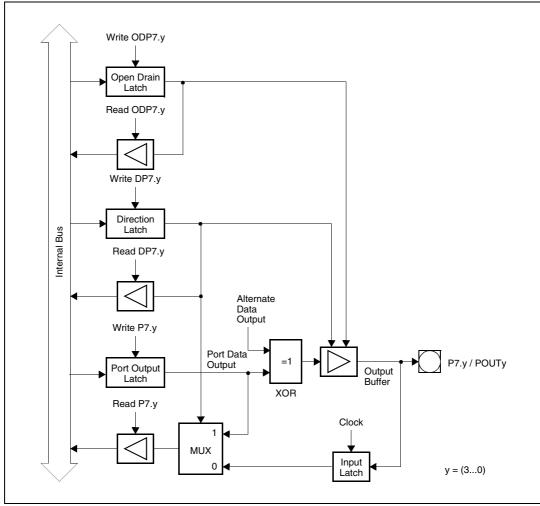

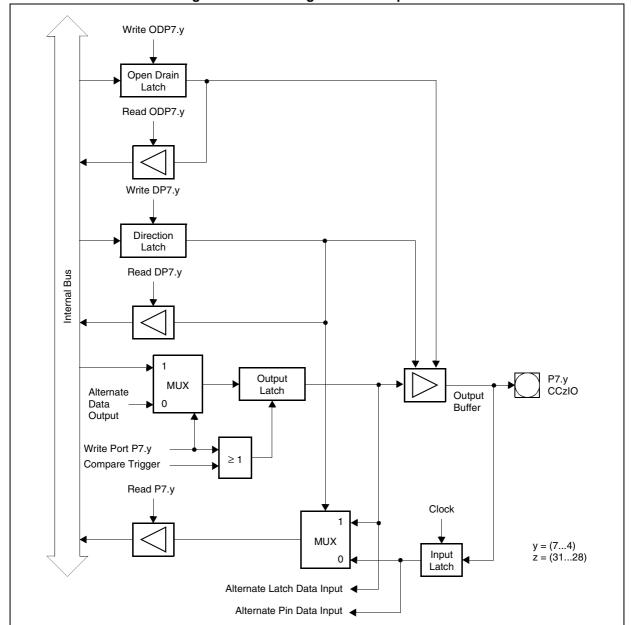

|   | 0.5                        | 6.9.1    | Alternate functions of Port7                  |     |  |  |

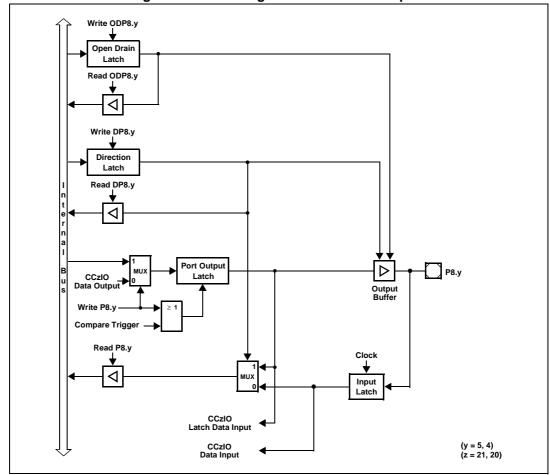

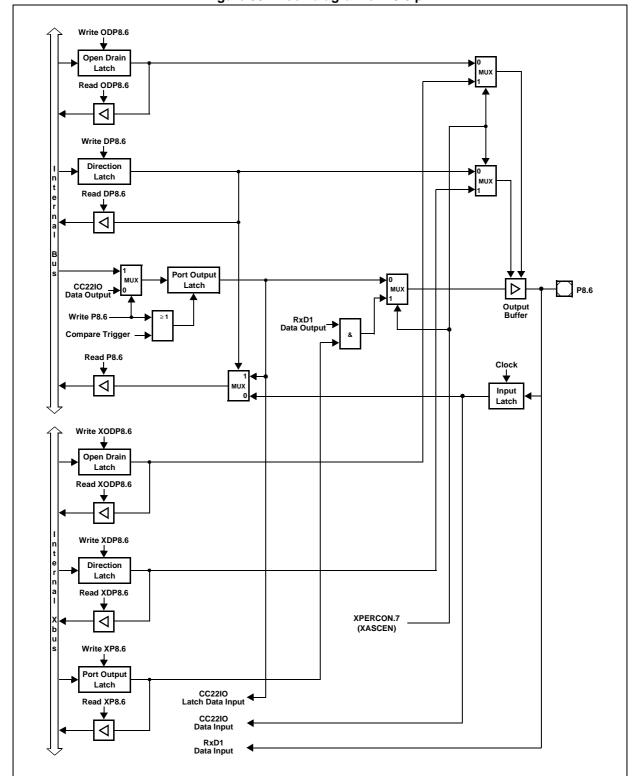

|   | 6.10                       |          | Alternate functions of Forth                  |     |  |  |

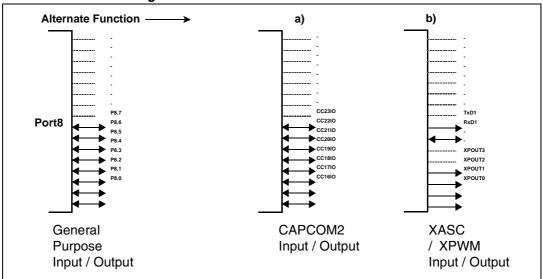

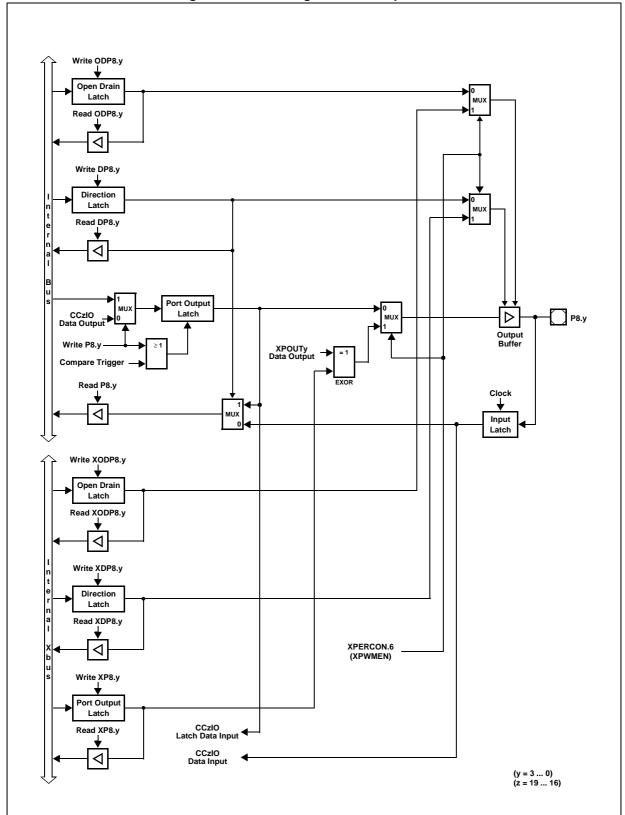

|   | 6.10                       | 6.10.1   | Alternate functions of Port8                  |     |  |  |

|   |                            | 0.10.1   | Alternate functions of Forto                  | 174 |  |  |

| 7 | Dedi                       | cated pi | ins                                           | 179 |  |  |

|   |                            |          |                                               |     |  |  |

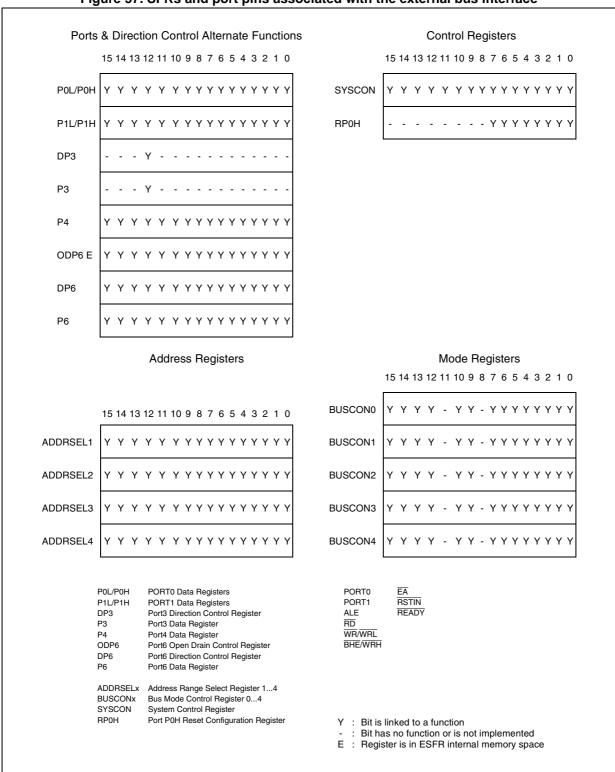

| 8 | The external bus interface |          |                                               |     |  |  |

|   | 8.1                        | Single   | chip mode                                     | 181 |  |  |

|   | 8.2                        | Externa  | al bus modes                                  | 183 |  |  |

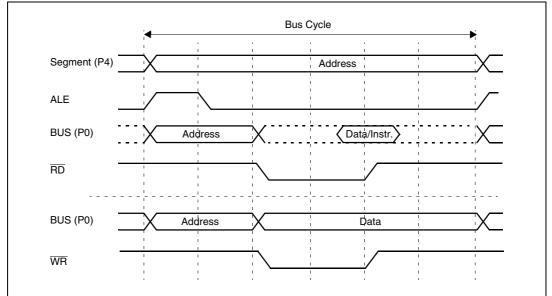

|   |                            | 8.2.1    | Multiplexed bus modes                         | 183 |  |  |

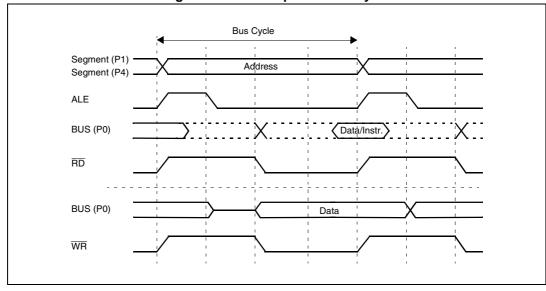

|   |                            | 8.2.2    | De-multiplexed bus modes                      | 184 |  |  |

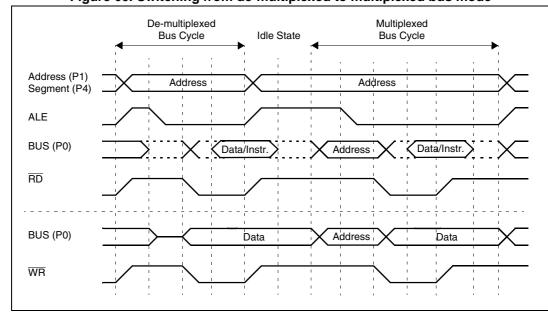

|   |                            | 8.2.3    | Switching between the bus modes               | 185 |  |  |

|   |                            | 8.2.4    | External data bus width                       | 186 |  |  |

|   |                            | 8.2.5    | Disable / enable control for pin BHE (BYTDIS) | 187 |  |  |

|   |                            | 8.2.6    | Segment address generation                    | 187 |  |  |

|   |                            | 8.2.7    | CS signal generation                          | 188 |  |  |

|   |                            | 8.2.8    | Segment address versus chip select            | 189 |  |  |

|   | 8.3                        | Progra   | mmable bus characteristics                    | 190 |  |  |

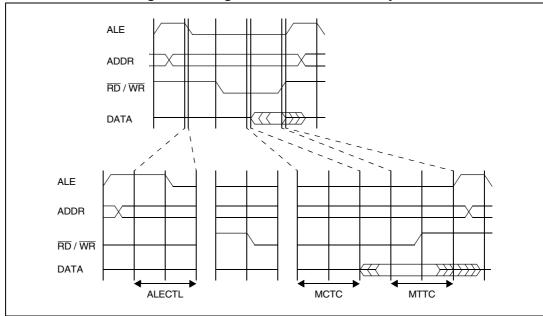

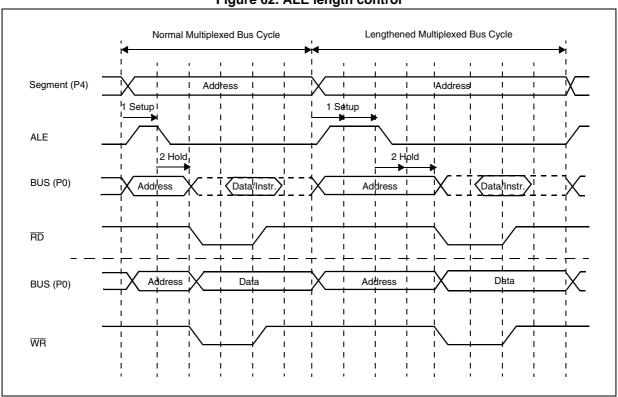

|   |                            | 8.3.1    | ALE length control                            | 190 |  |  |

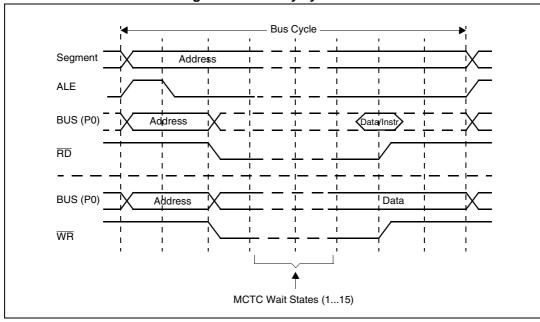

|   |                            | 8.3.2    | Programmable memory cycle time                | 191 |  |  |

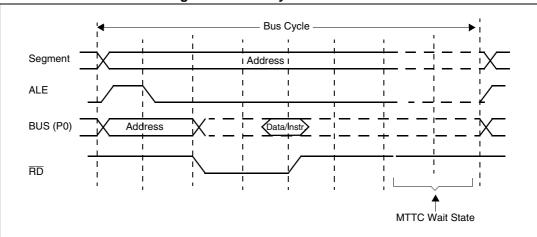

|   |                            | 8.3.3    | Programmable memory tri-state time            | 192 |  |  |

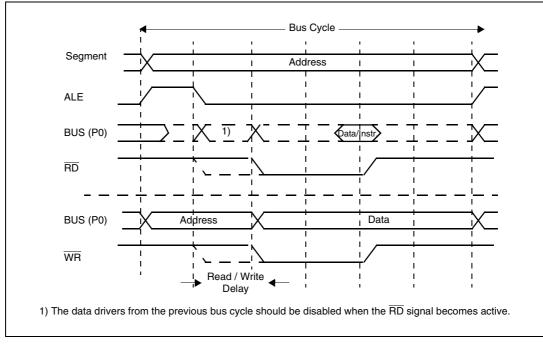

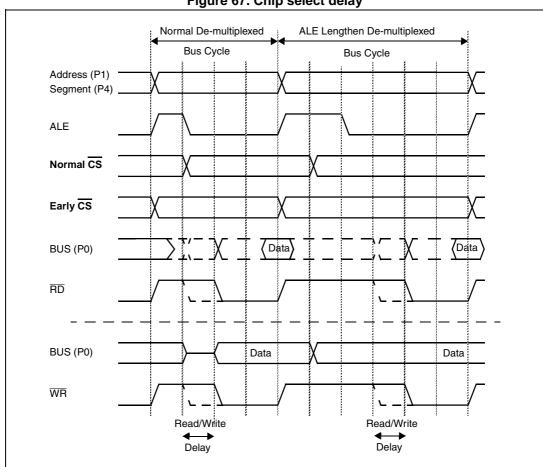

|   |                            | 8.3.4    | Read / write signal delay                     | 193 |  |  |

|   |                            | 8.3.5    | READY polarity                                | 194 |  |  |

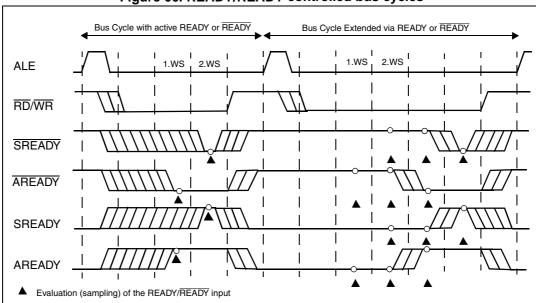

|   |                            | 8.3.6    | READY / READY controlled bus cycles           | 194 |  |  |

|   |                            | 8.3.7    | Programmable chip select timing control       | 196 |  |  |

|   | 8.4                        | Control  | lling the external bus controller             | 196 |  |  |

|   |                            | 8.4.1    | Definition of address areas                   | 201 |  |  |

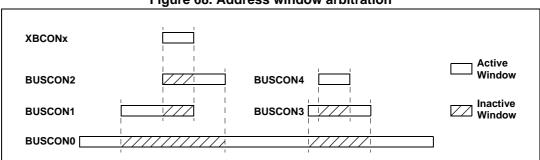

|   |                            | 8.4.2    | Address window arbitration                    | 201 |  |  |

|   |                            | 8.4.3    | Precautions and hints                         | 203 |  |  |

|   | 8.5                        | EBC id   | le state                                      | 203 |  |  |

|   | 8.6                        | Externa  | al bus arbitration                            | 204 |  |  |

|   |                            |          |                                               |     |  |  |

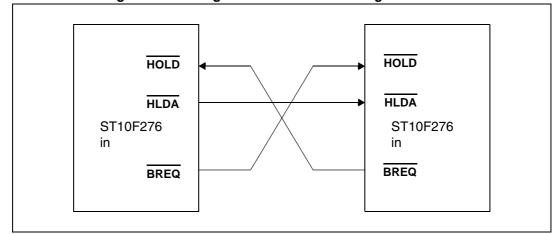

|    |       | 8.6.1   | Connecting bus masters                       | 204 |

|----|-------|---------|----------------------------------------------|-----|

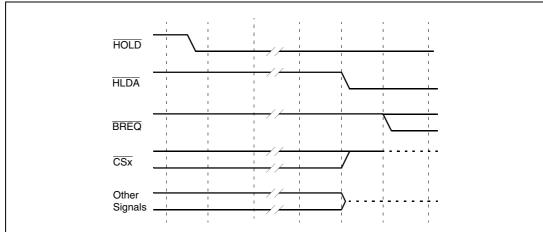

|    |       | 8.6.2   | Entering the hold state                      | 205 |

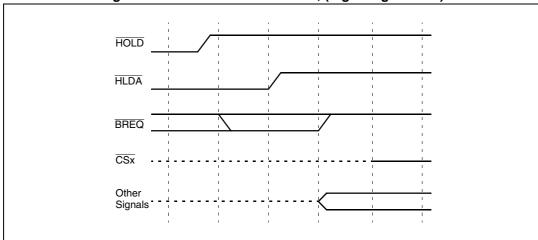

|    |       | 8.6.3   | Exiting the hold state                       | 206 |

|    | 8.7   | The XI  | BUS interface                                | 207 |

|    | 8.8   | EA fun  | nctionality                                  | 213 |

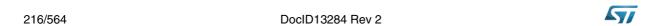

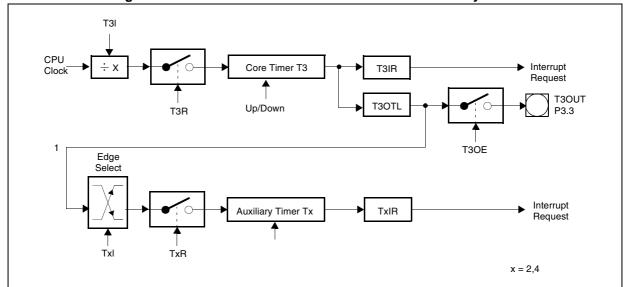

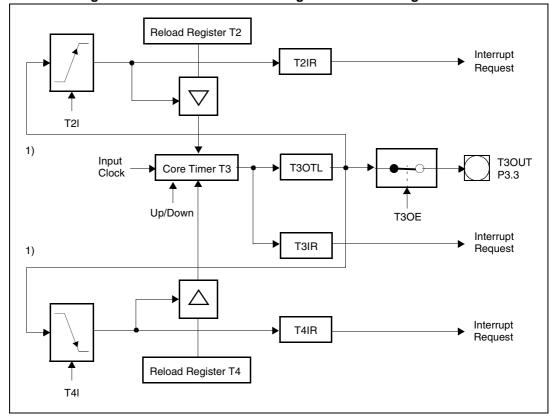

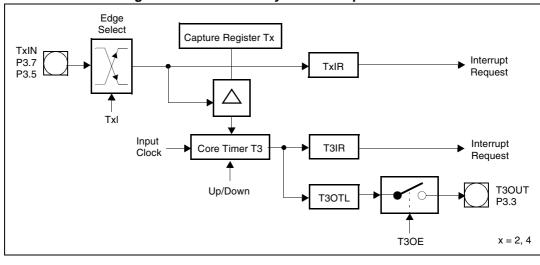

| 9  | The g | general | purpose timer units                          | 215 |

|    | 9.1   | Timer I | block GPT1                                   | 215 |

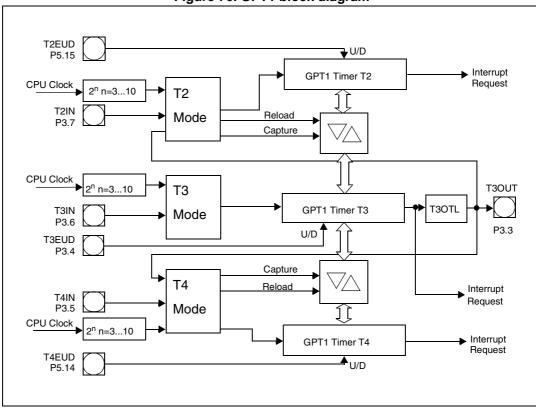

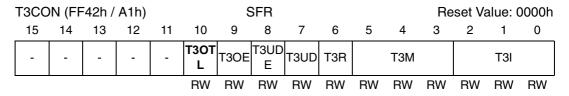

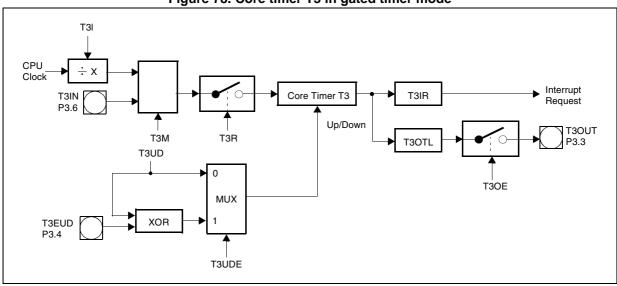

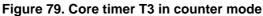

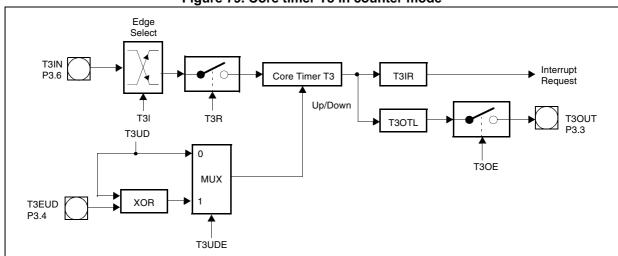

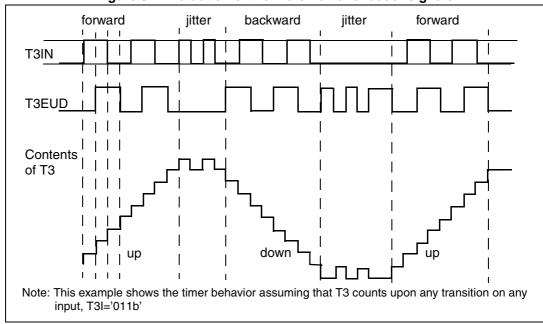

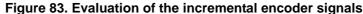

|    |       | 9.1.1   | GPT1 core timer T3                           | 217 |

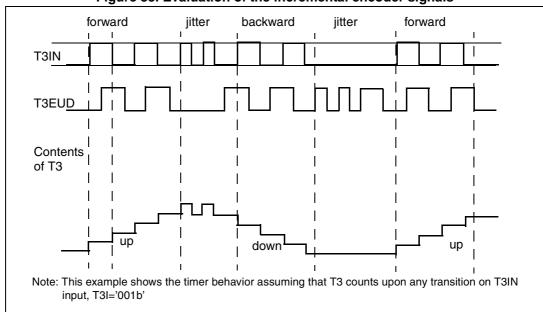

|    |       | 9.1.2   | GPT1 auxiliary timers T2 and T4              | 224 |

|    |       | 9.1.3   | Interrupt control for GPT1 timers            | 231 |

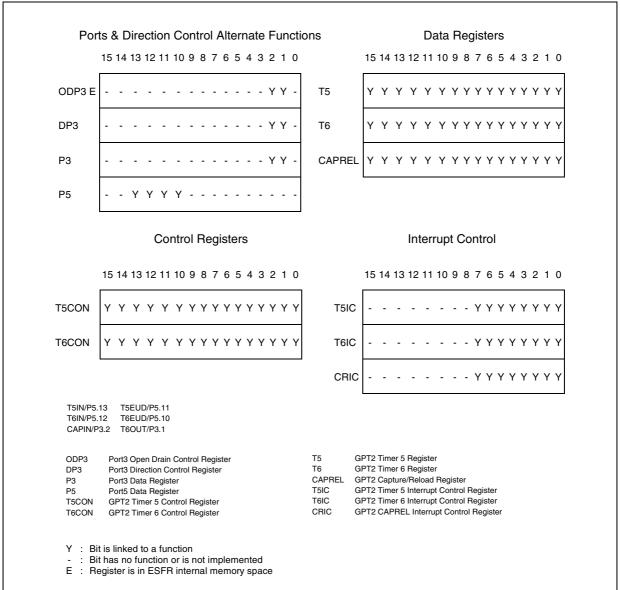

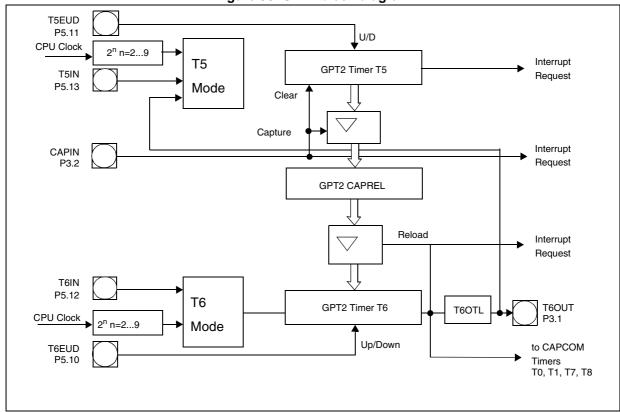

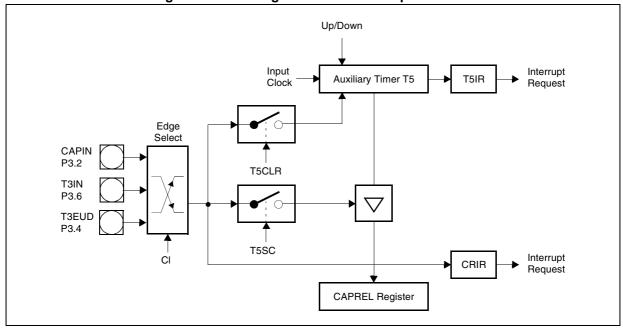

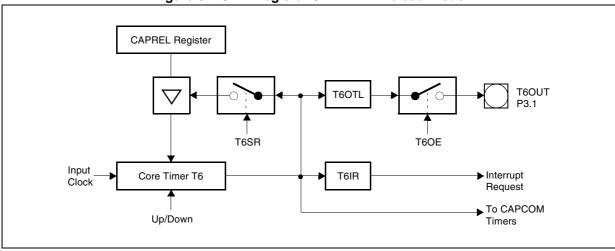

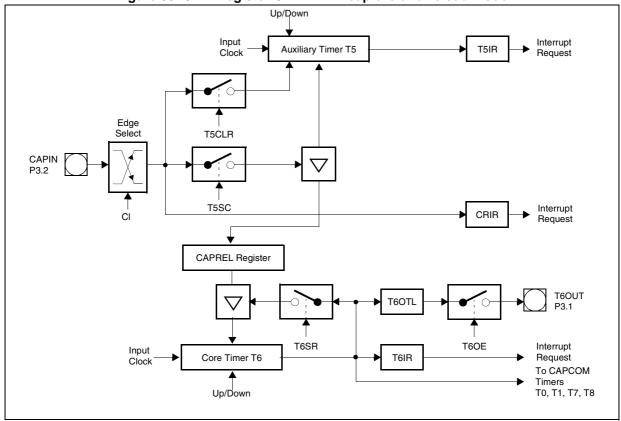

|    | 9.2   | Timer I | block GPT2                                   | 232 |

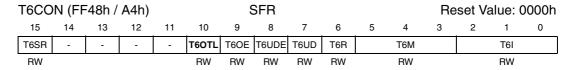

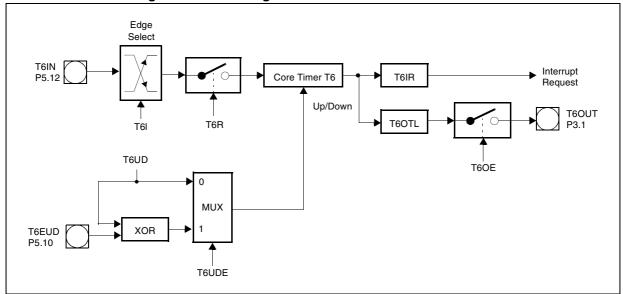

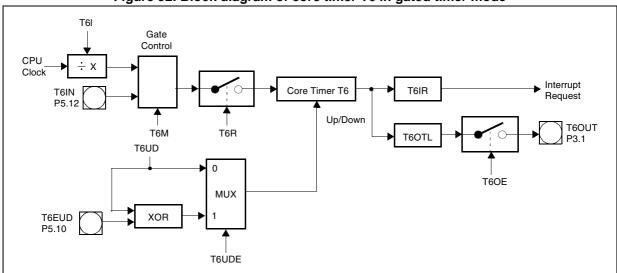

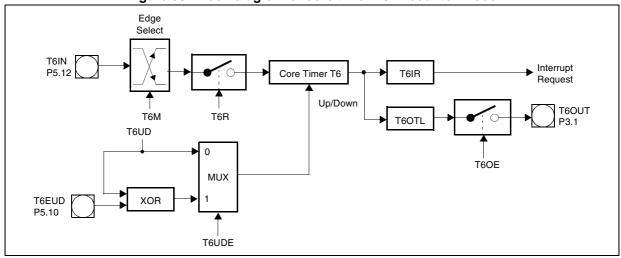

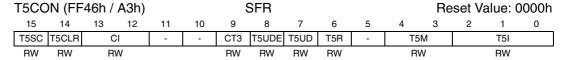

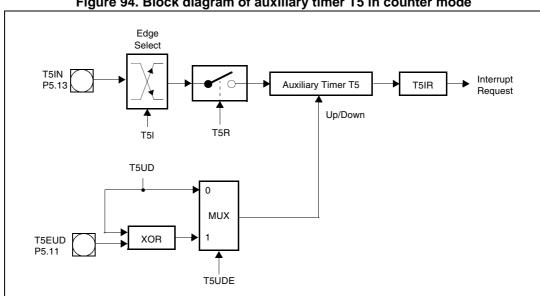

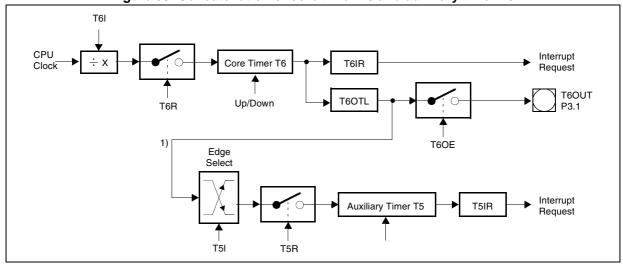

|    |       | 9.2.1   | GPT2 core timer T6                           | 234 |

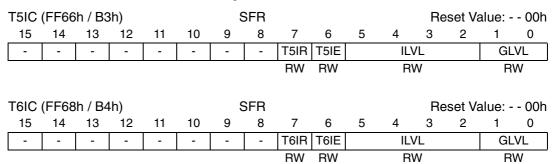

|    |       | 9.2.2   | Interrupt control for GPT2 timers and CAPREL | 244 |

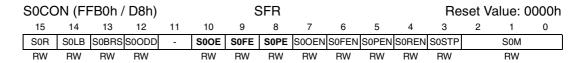

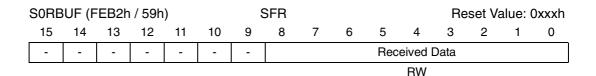

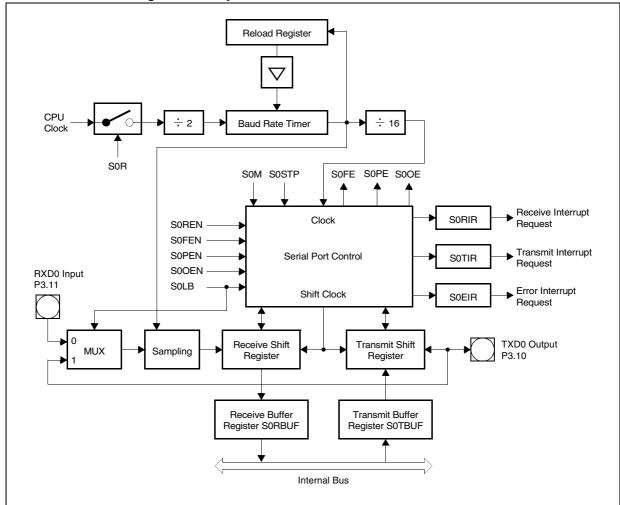

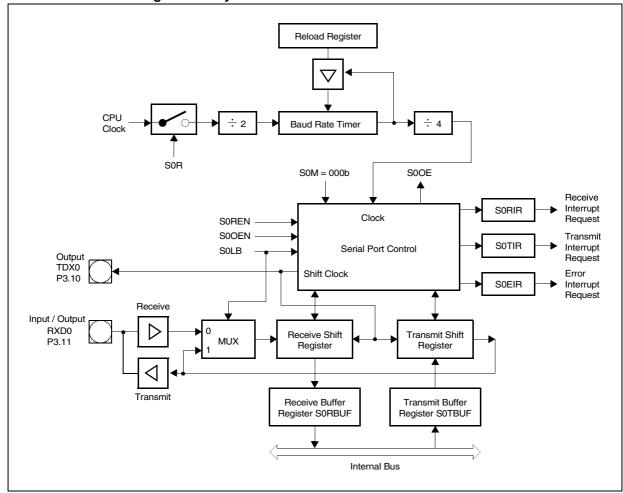

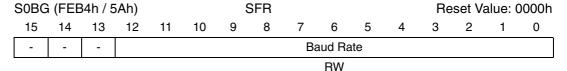

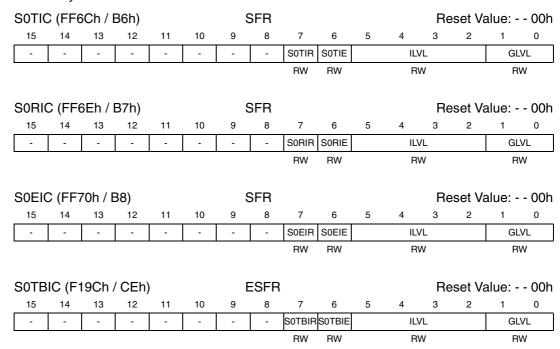

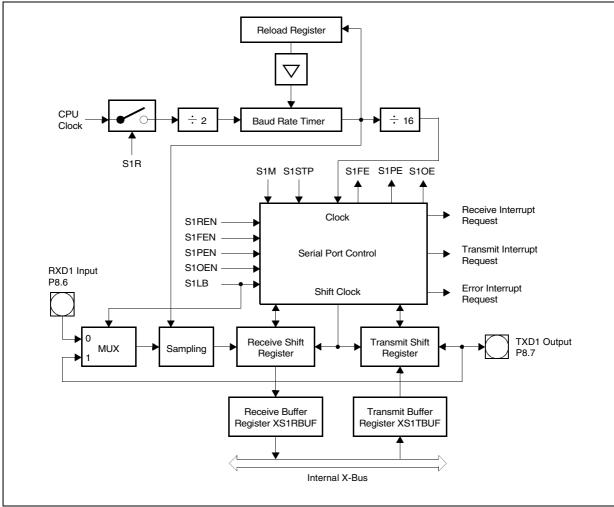

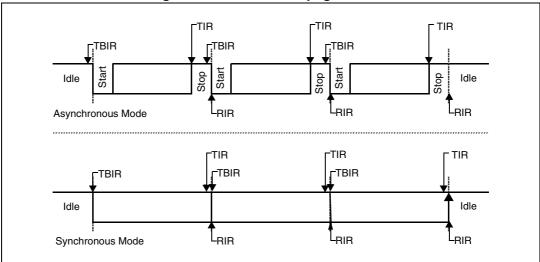

| 10 | Asyn  | chrono  | ous / synchronous serial interface           | 246 |

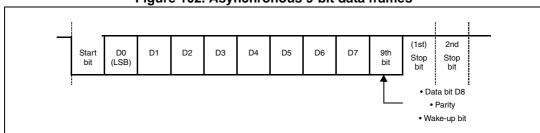

|    | 10.1  | Asynch  | hronous operation                            | 249 |

|    | 10.2  | Synch   | ronous operation                             | 251 |

|    | 10.3  | Hardw   | are error detection                          | 253 |

|    | 10.4  | ASC0    | baud rate generation                         | 253 |

|    | 10.5  | ASC0    | interrupt control                            | 254 |

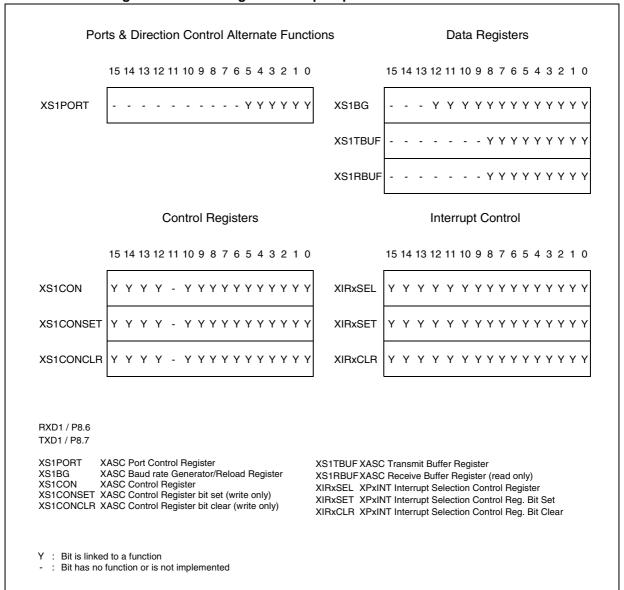

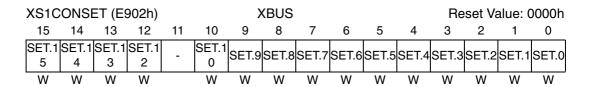

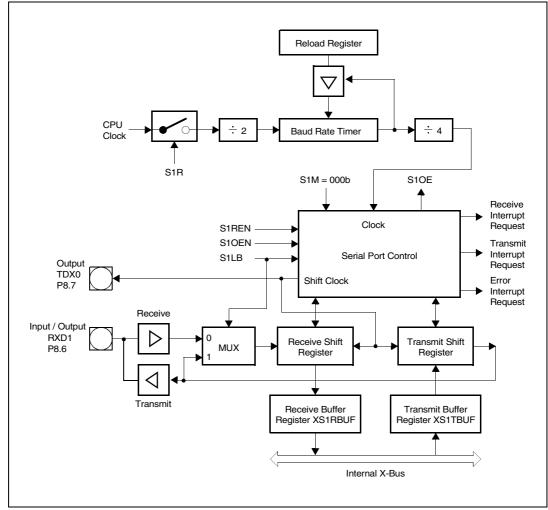

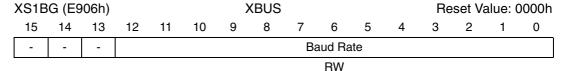

| 11 | XBU   | S asyno | chronous / synchronous serial interface      | 257 |

|    | 11.1  | Asynch  | hronous operation                            | 261 |

|    | 11.2  | Synchi  | ronous operation                             | 264 |

|    | 11.3  | Hardw   | rare error detection                         | 266 |

|    | 11.4  | XASC    | baud rate generation                         | 266 |

|    | 11.5  | XASC    | interrupt control                            | 267 |

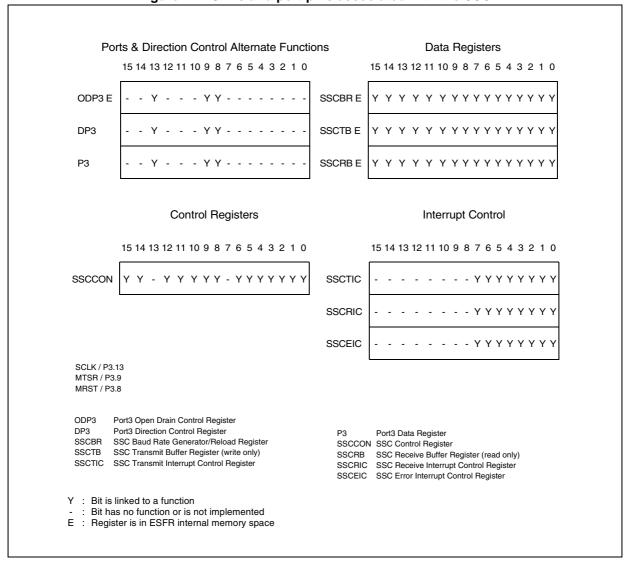

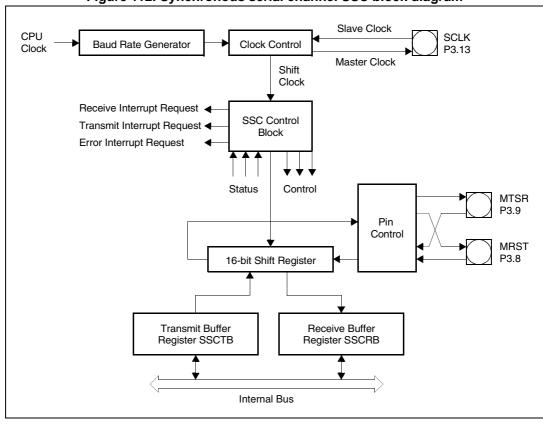

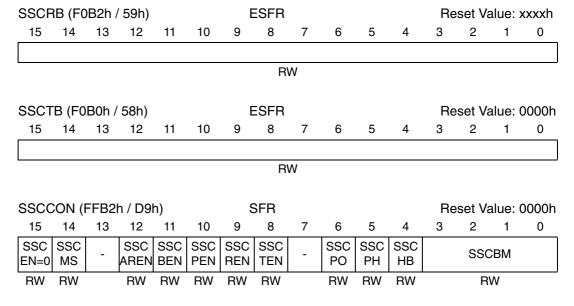

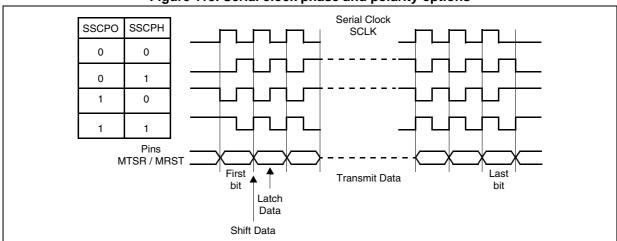

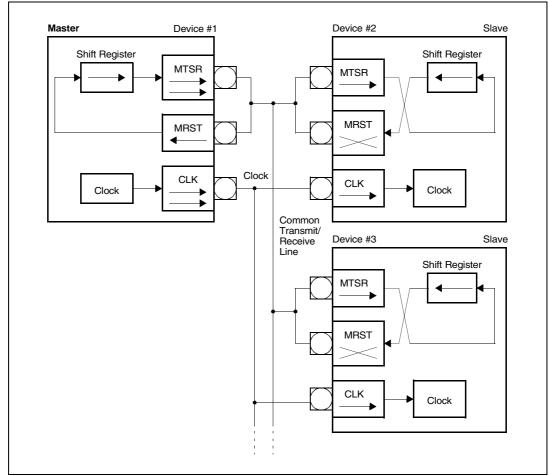

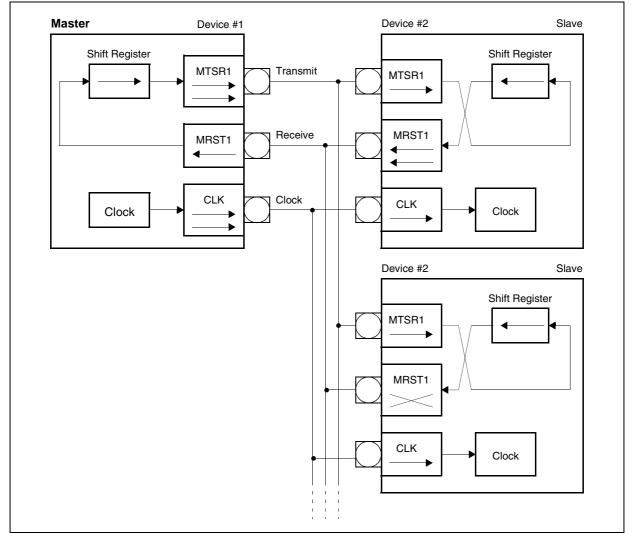

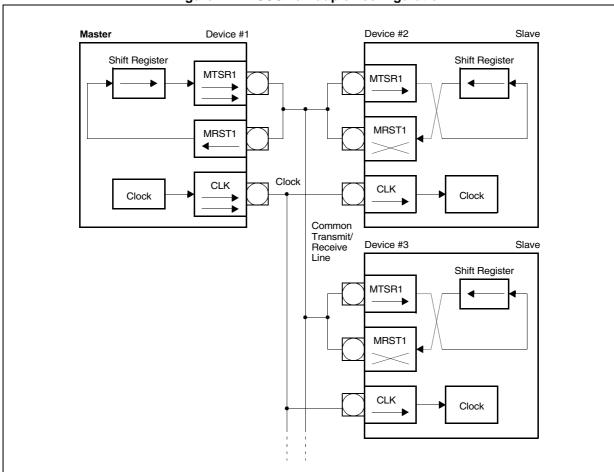

| 12 | High- | -speed  | synchronous serial interface                 | 270 |

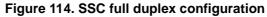

|    | 12.1  | Full-du | uplex operation                              | 275 |

|    | 12.2  | Half du | uplex operation                              | 278 |

|    |       | 12.2.1  | Port control                                 |     |

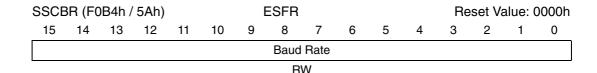

|    | 12.3  | Baud r  | rate generation                              |     |

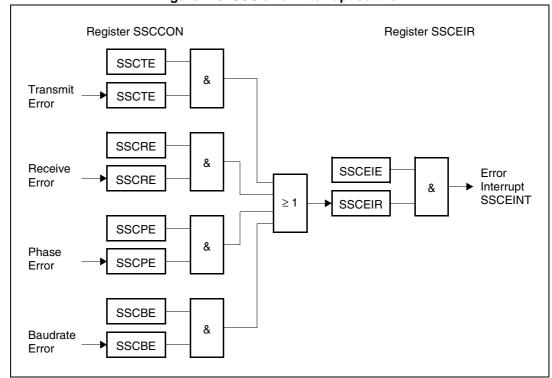

|    | 12.4  |         | detection mechanisms                         |     |

|    |       |         |                                              |     |

|    | 12.5                 | SSC in  | nterrupt control                                    | 282 |  |  |  |

|----|----------------------|---------|-----------------------------------------------------|-----|--|--|--|

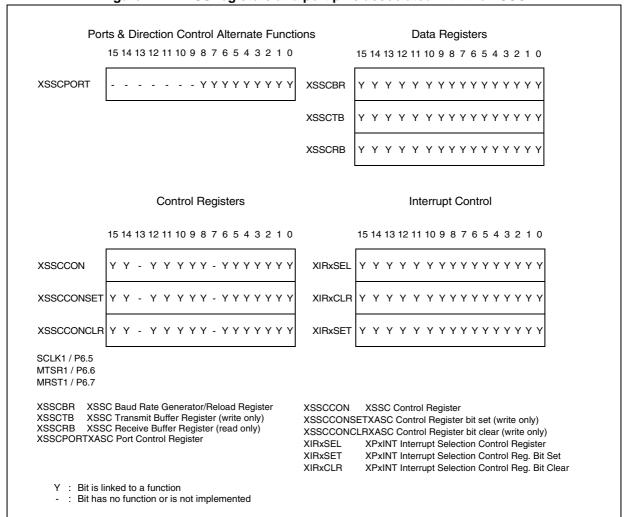

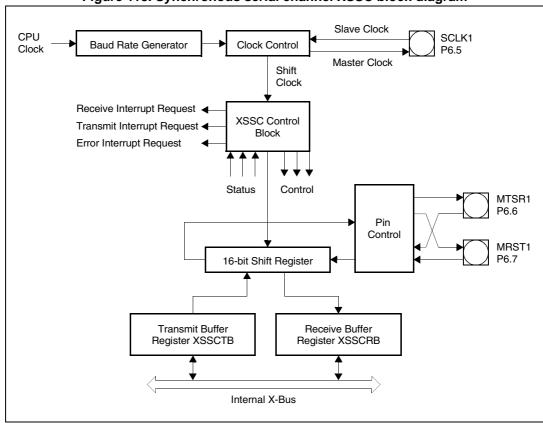

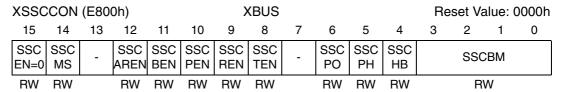

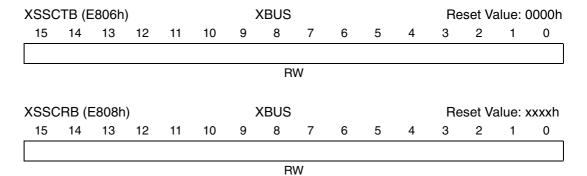

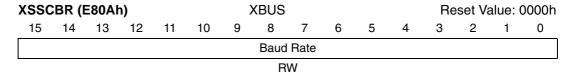

| 13 | XBU                  | S high- | speed synchronous serial interface                  | 284 |  |  |  |

|    | 13.1                 | Full-du | plex operation                                      | 290 |  |  |  |

|    | 13.2                 | Half du | uplex operation                                     | 293 |  |  |  |

|    |                      | 13.2.1  | Port control                                        | 294 |  |  |  |

|    | 13.3                 | Baud r  | ate generation                                      | 294 |  |  |  |

|    | 13.4                 | Error d | letection mechanisms                                | 295 |  |  |  |

|    | 13.5                 | XSSC    | interrupt control                                   | 296 |  |  |  |

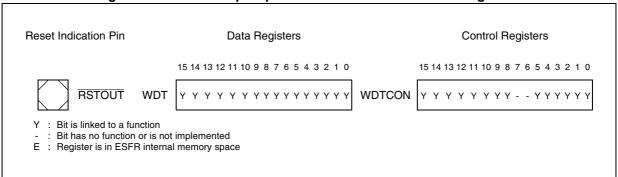

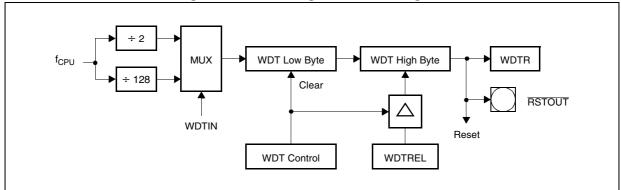

| 14 | Watc                 | hdog ti | mer                                                 | 297 |  |  |  |

|    | 14.1                 | Operat  | tion of the watchdog timer                          | 298 |  |  |  |

| 15 | The bootstrap loader |         |                                                     |     |  |  |  |

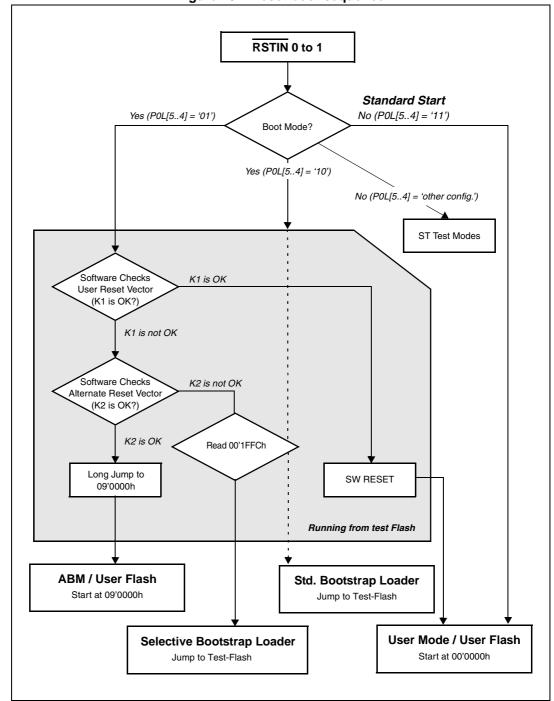

|    | 15.1                 | Selecti | on among user-code, standard or alternate bootstrap | 302 |  |  |  |

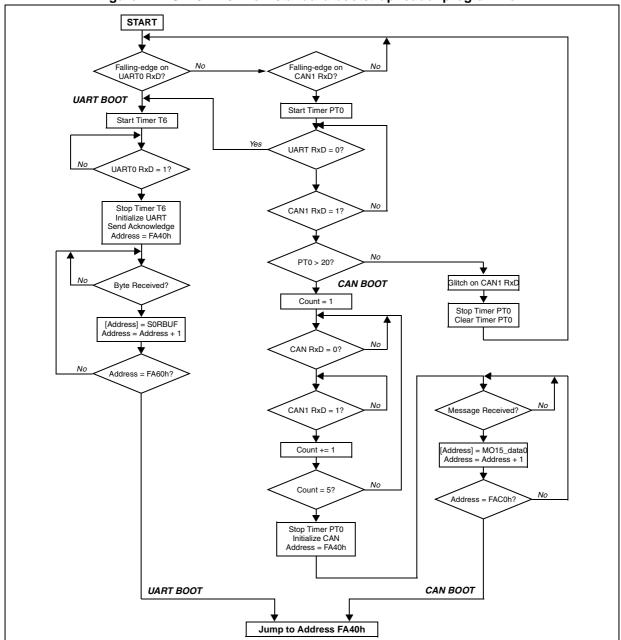

|    | 15.2                 | Standa  | urd bootstrap loader                                | 303 |  |  |  |

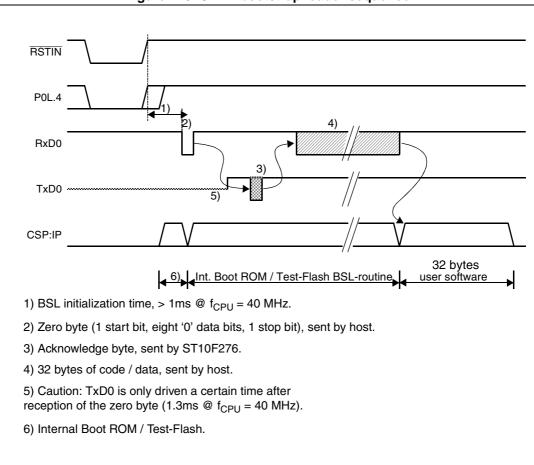

|    |                      | 15.2.1  | Entering the standard bootstrap loader              | 303 |  |  |  |

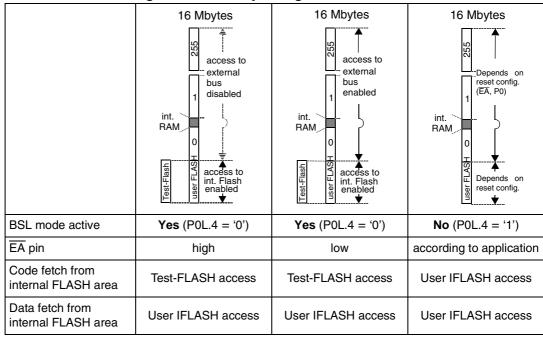

|    |                      | 15.2.2  | ST10 configuration in BSL                           | 305 |  |  |  |

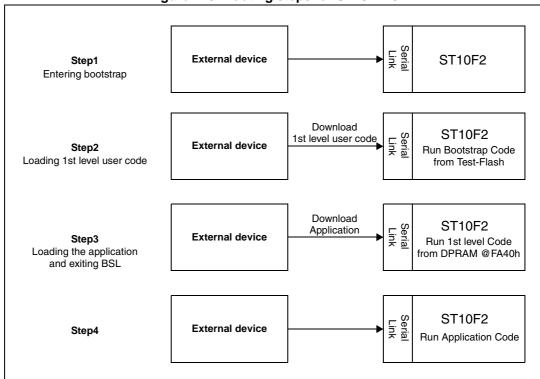

|    |                      | 15.2.3  | Booting steps                                       | 305 |  |  |  |

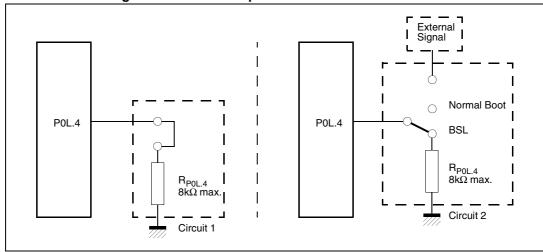

|    |                      | 15.2.4  | Hardware to activate BSL                            | 306 |  |  |  |

|    |                      | 15.2.5  | Memory configuration in bootstrap loader mode       | 307 |  |  |  |

|    |                      | 15.2.6  | Loading the start-up code                           | 308 |  |  |  |

|    |                      | 15.2.7  | Exiting bootstrap loader mode                       | 308 |  |  |  |

|    |                      | 15.2.8  | Hardware requirements                               | 309 |  |  |  |

|    | 15.3                 | Standa  | ard bootstrap with UART (RS232 or K-Line)           | 309 |  |  |  |

|    |                      | 15.3.1  | Features                                            | 309 |  |  |  |

|    |                      | 15.3.2  | Entering bootstrap via UART                         | 310 |  |  |  |

|    |                      | 15.3.3  | ST10 configuration in UART BSL (RS232 or K-line)    | 310 |  |  |  |

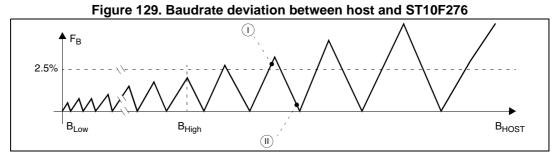

|    |                      | 15.3.4  | Loading the start-up code                           | 311 |  |  |  |

|    |                      | 15.3.5  | Choosing the baud rate for the BSL via UART         | 312 |  |  |  |

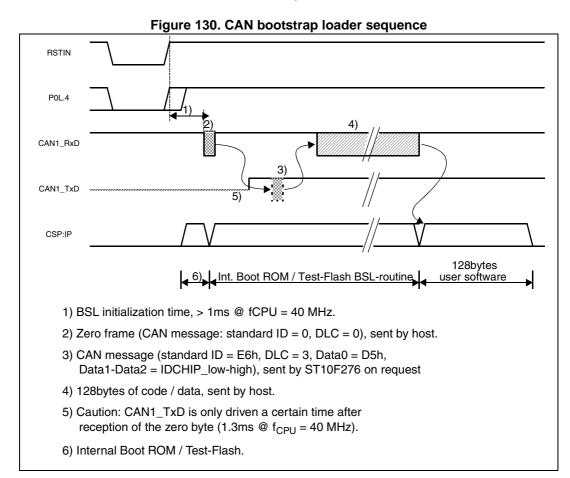

|    | 15.4                 | Standa  | ard bootstrap with CAN                              | 313 |  |  |  |

|    |                      | 15.4.1  | Features                                            | 313 |  |  |  |

|    |                      | 15.4.2  | Entering the CAN bootstrap loader                   | 314 |  |  |  |

|    |                      | 15.4.3  | ST10 configuration in CAN BSL                       | 315 |  |  |  |

|    |                      | 15.4.4  | Loading the start-up code via CAN                   | 315 |  |  |  |

|    |                      | 15.4.5  | Choosing the baudrate for the BSL via CAN           | 316 |  |  |  |

|    |                      |         |                                                     |     |  |  |  |

|    |       | 15.4.6   | How to compute the baud rate error            | . 318 |

|----|-------|----------|-----------------------------------------------|-------|

|    |       | 15.4.7   | Bootstrap via CAN                             | . 319 |

|    | 15.5  | Compa    | ring the old and the new bootstrap loader     | 319   |

|    |       | 15.5.1   | Software aspects                              | . 319 |

|    |       | 15.5.2   | Hardware aspects                              | . 320 |

|    | 15.6  | Alternat | te boot mode (ABM)                            | 320   |

|    |       | 15.6.1   | Activation                                    | . 320 |

|    |       | 15.6.2   | Memory mapping                                | . 320 |

|    |       | 15.6.3   | Interrupts                                    | . 320 |

|    |       | 15.6.4   | ST10 configuration in alternate boot mode     | . 321 |

|    |       | 15.6.5   | Watchdog                                      | . 321 |

|    |       | 15.6.6   | Exiting alternate boot mode                   | . 321 |

|    |       | 15.6.7   | Alternate boot user software                  | . 322 |

|    |       | 15.6.8   | User/alternate mode signature integrity check | . 322 |

|    |       | 15.6.9   | Alternate boot user software aspects          | . 322 |

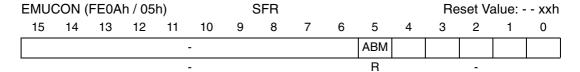

|    |       | 15.6.10  | EMUCON register                               | . 322 |

|    |       | 15.6.11  | Internal decoding of test modes               | . 323 |

|    |       | 15.6.12  | Example                                       | . 323 |

|    | 15.7  | Selectiv | ve boot mode                                  | 323   |

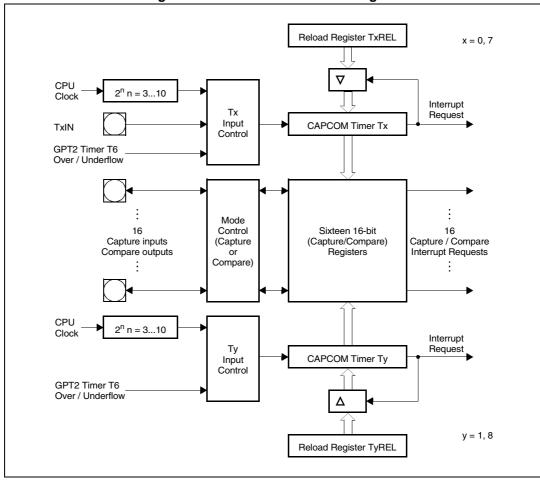

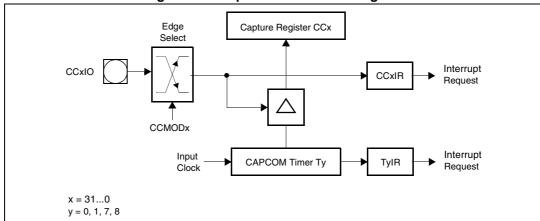

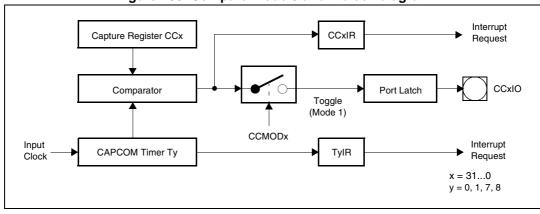

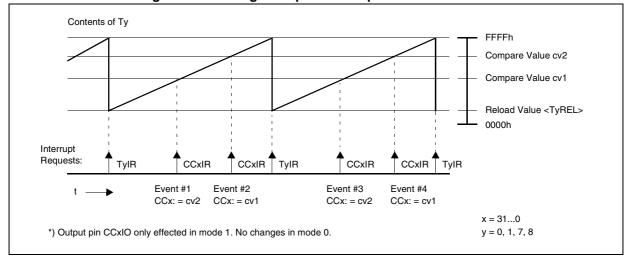

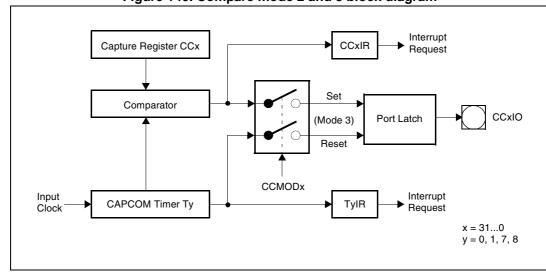

| 16 | The c | apture   | / compare units                               | 326   |

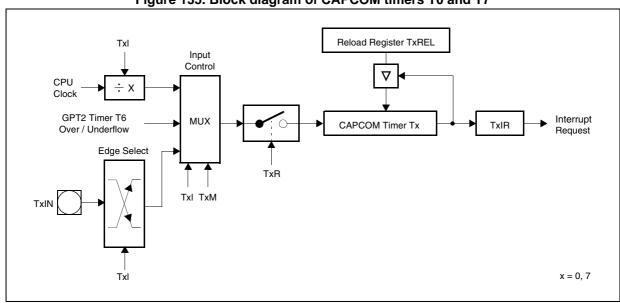

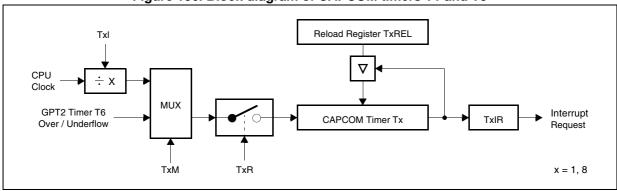

|    | 16.1  | CAPCO    | DM timers                                     | 329   |

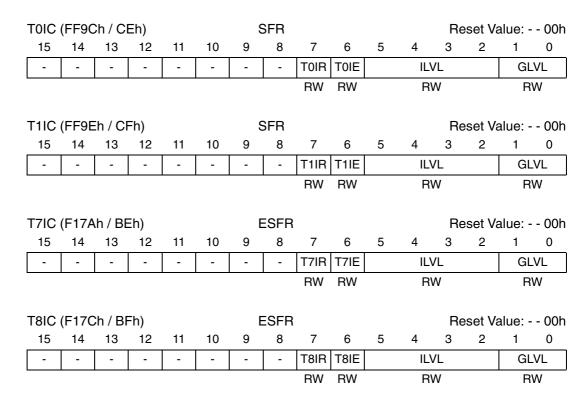

|    | 16.2  | CAPCO    | OM unit timer interrupts                      | 333   |

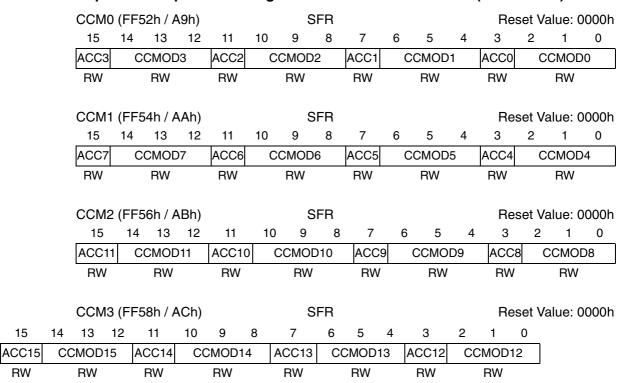

|    | 16.3  |          | e / compare registers                         |       |

|    |       | 16.3.1   | Selection of capture modes and compare modes  |       |

|    | 16.4  | Capture  | e mode                                        |       |

|    | 16.5  | •        | re modes                                      |       |

|    |       | 16.5.1   | Compare mode 0                                |       |

|    |       | 16.5.2   | Compare mode 1                                |       |

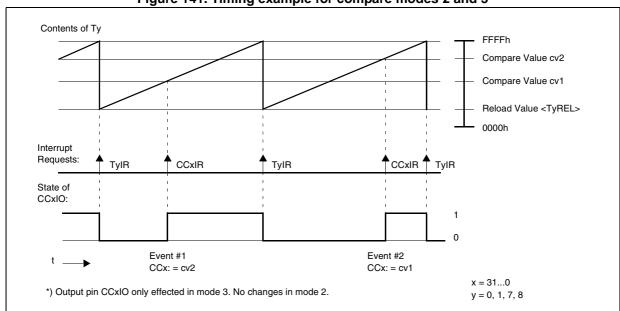

|    |       | 16.5.3   | Compare mode 2                                |       |

|    |       | 16.5.4   | Compare mode 3                                | . 340 |

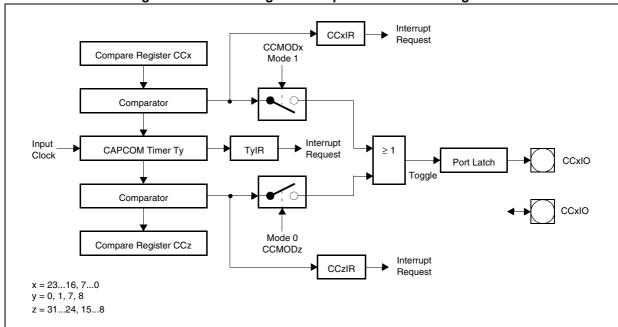

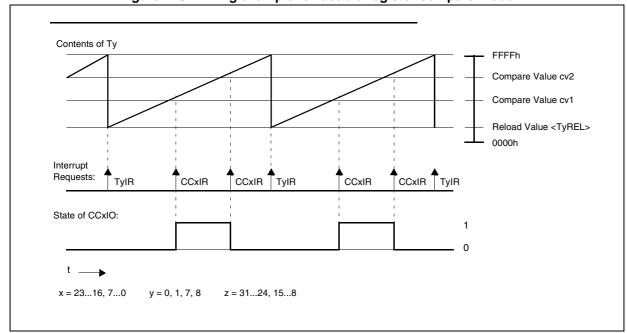

|    |       | 16.5.5   | Double register compare mode                  | . 341 |

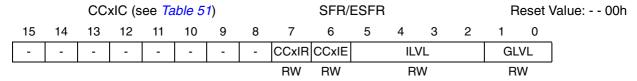

|    | 16.6  | Capture  | e / compare interrupts                        | 343   |

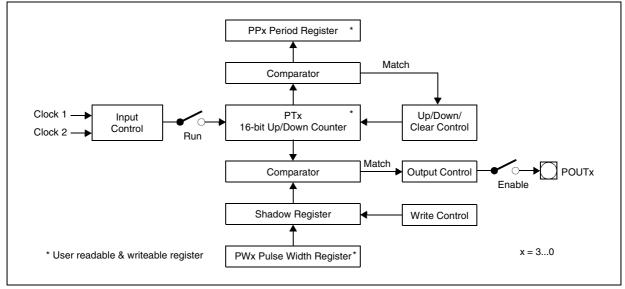

| 17 | Pulse | width i  | modulation module                             | 345   |

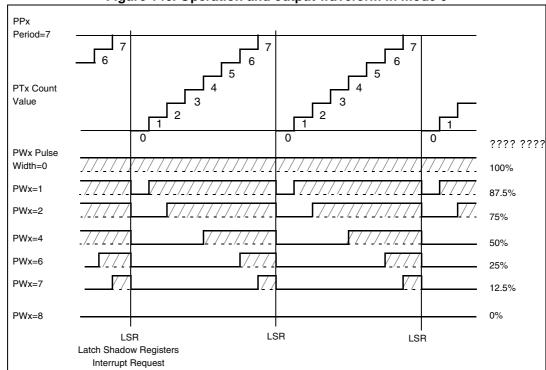

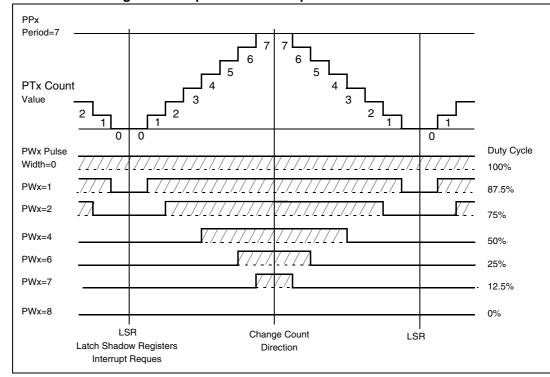

|    | 17.1  |          | ng modes                                      |       |

|    |       |          |                                               |       |

|    |                      |                                                                                                                          | Mode 0: standard PWM generation (edge aligned PWM)                                                                                                                                                                                             | 347                                           |

|----|----------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|    |                      | 17.1.2                                                                                                                   | Mode 1: symmetrical PWM generation (center aligned PWM)                                                                                                                                                                                        | 348                                           |

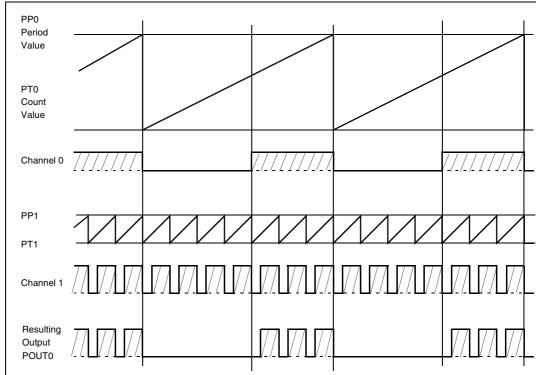

|    |                      | 17.1.3                                                                                                                   | Burst mode                                                                                                                                                                                                                                     | 349                                           |

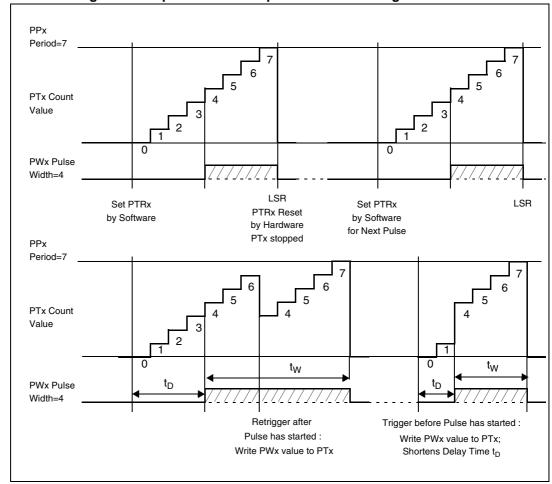

|    |                      | 17.1.4                                                                                                                   | Single shot mode                                                                                                                                                                                                                               | 350                                           |

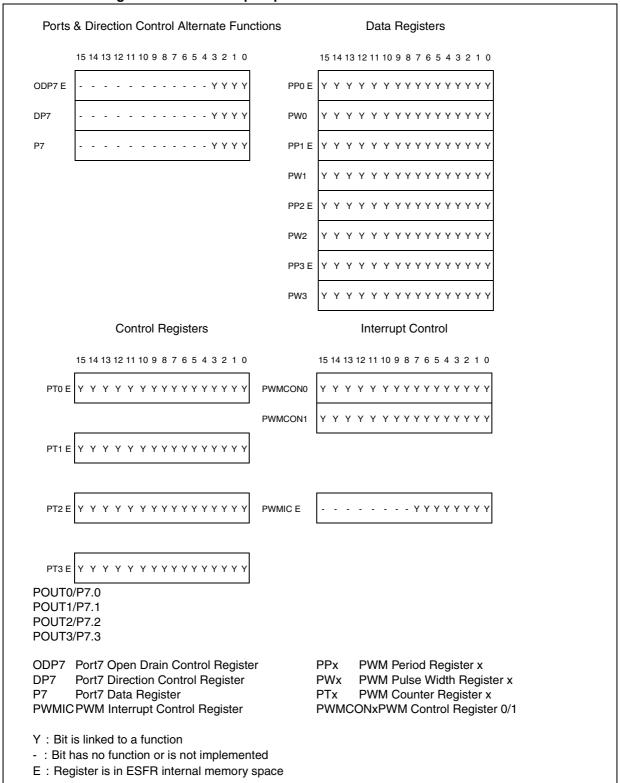

|    | 17.2                 | PWM n                                                                                                                    | nodule registers                                                                                                                                                                                                                               | 351                                           |

|    | 17.3                 | Interrup                                                                                                                 | ot request generation                                                                                                                                                                                                                          | 354                                           |

|    | 17.4                 | PWM o                                                                                                                    | utput signals                                                                                                                                                                                                                                  | 355                                           |

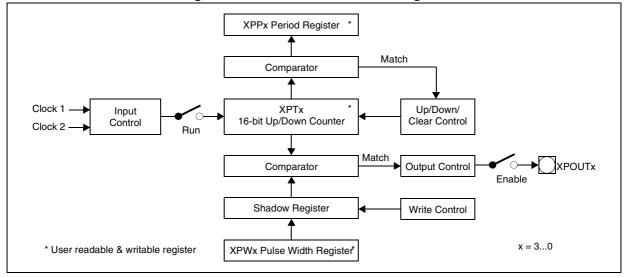

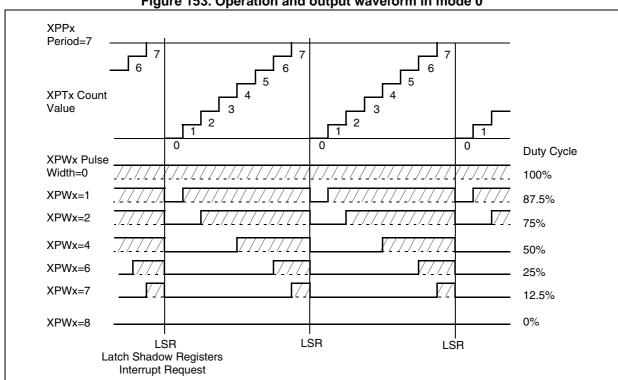

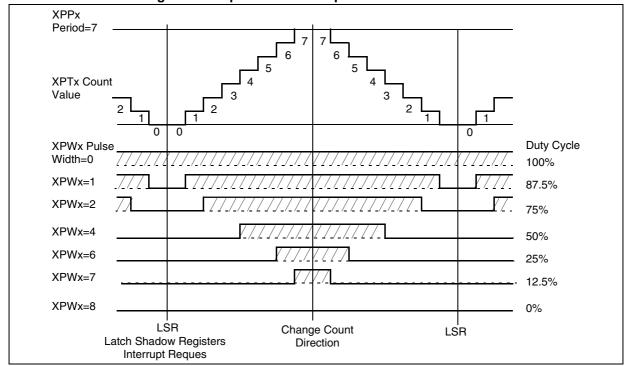

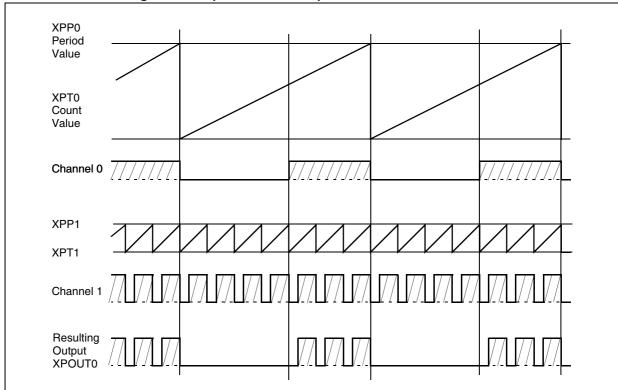

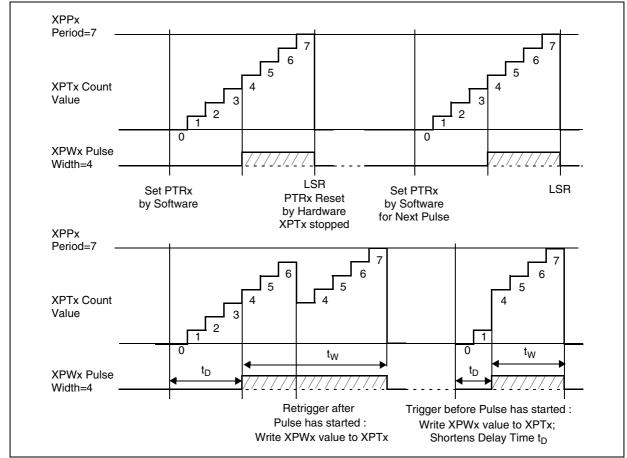

| 18 | XBU                  | S pulse                                                                                                                  | width modulation module                                                                                                                                                                                                                        | 357                                           |

|    | 18.1                 | Operati                                                                                                                  | ng modes                                                                                                                                                                                                                                       | 359                                           |

|    |                      | 18.1.1                                                                                                                   | Mode 0: standard PWM generation (edge aligned PWM)                                                                                                                                                                                             | 359                                           |

|    |                      | 18.1.2                                                                                                                   | Mode 1: symmetrical PWM generation (center aligned PWM)                                                                                                                                                                                        | 360                                           |

|    |                      | 18.1.3                                                                                                                   | Burst mode                                                                                                                                                                                                                                     | 361                                           |

|    |                      | 18.1.4                                                                                                                   | Single shot mode                                                                                                                                                                                                                               | 362                                           |

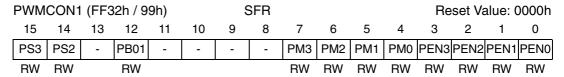

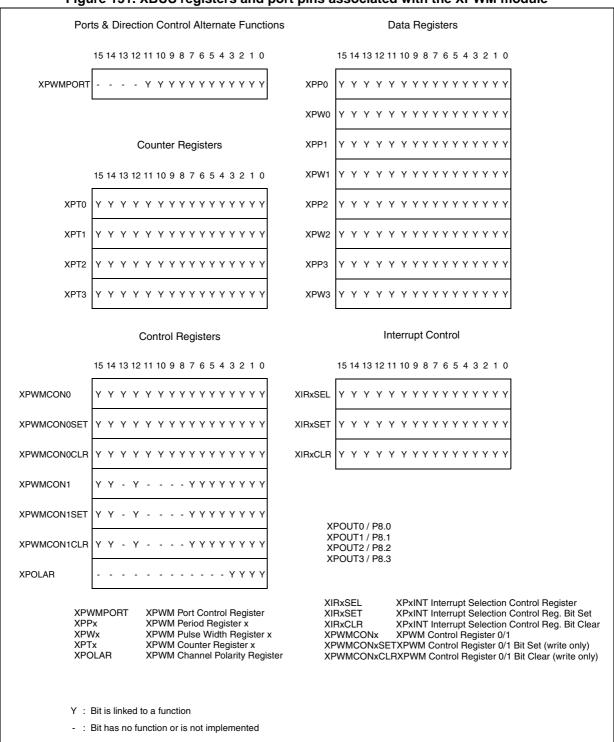

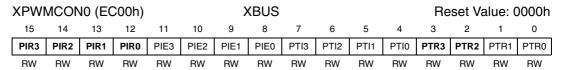

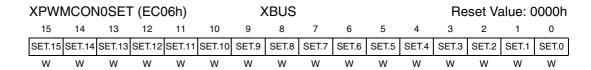

|    | 18.2                 | XPWM                                                                                                                     | module registers                                                                                                                                                                                                                               | 363                                           |

|    | 18.3                 | Interrup                                                                                                                 | ot request generation                                                                                                                                                                                                                          | 367                                           |

|    | 18.4                 | XPWM                                                                                                                     | output signals                                                                                                                                                                                                                                 | 368                                           |

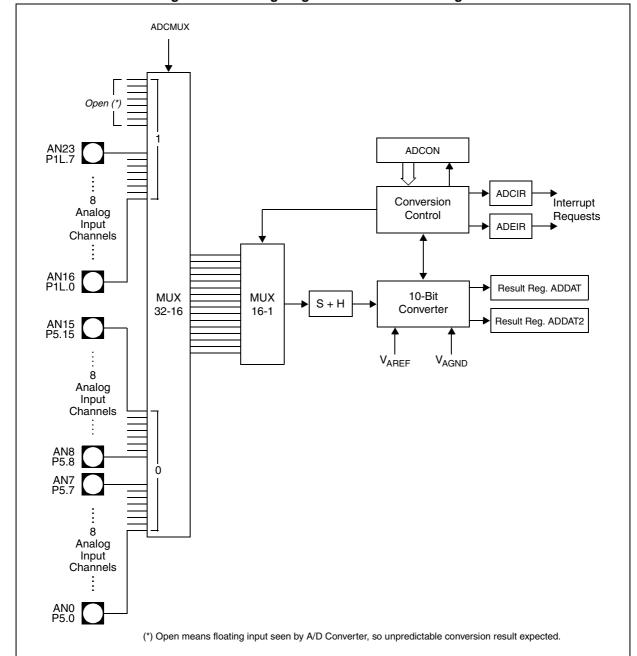

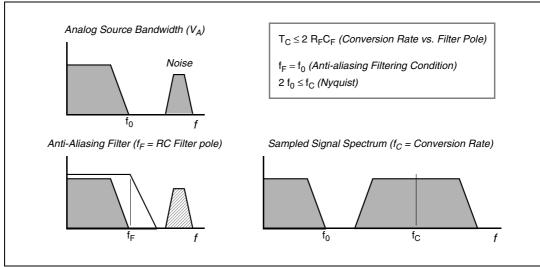

| 19 | Anal                 | og / digi                                                                                                                | tal converter                                                                                                                                                                                                                                  | 370                                           |

|    | 19.1                 | Mode s                                                                                                                   | election and operation                                                                                                                                                                                                                         | 372                                           |

|    |                      | 19.1.1                                                                                                                   | Fixed channel conversion modes                                                                                                                                                                                                                 |                                               |

|    |                      | 19.1.1                                                                                                                   |                                                                                                                                                                                                                                                | 375                                           |

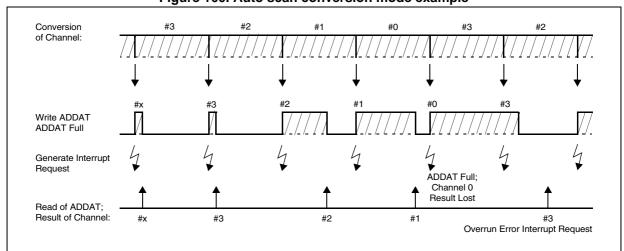

|    |                      | 19.1.1                                                                                                                   | Auto scan conversion modes                                                                                                                                                                                                                     |                                               |

|    |                      | _                                                                                                                        |                                                                                                                                                                                                                                                | 376                                           |

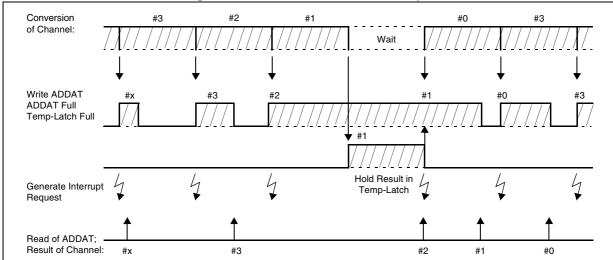

|    |                      | 19.1.2                                                                                                                   | Auto scan conversion modes                                                                                                                                                                                                                     | 376                                           |

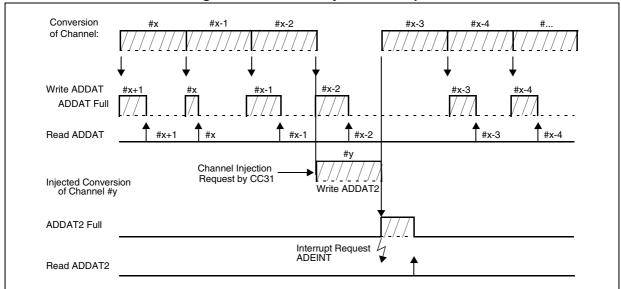

|    |                      | 19.1.2<br>19.1.3                                                                                                         | Auto scan conversion modes                                                                                                                                                                                                                     | 376<br>377<br>377                             |

|    | 19.2                 | 19.1.2<br>19.1.3<br>19.1.4<br>19.1.5                                                                                     | Auto scan conversion modes                                                                                                                                                                                                                     | 376<br>377<br>380                             |

|    | 19.2<br>19.3         | 19.1.2<br>19.1.3<br>19.1.4<br>19.1.5<br>Conver                                                                           | Auto scan conversion modes                                                                                                                                                                                                                     | 376<br>377<br>377<br>380                      |

|    |                      | 19.1.2<br>19.1.3<br>19.1.4<br>19.1.5<br>Conver<br>A/D cor                                                                | Auto scan conversion modes  Wait for ADDAT read mode  Channel injection mode  ADC power off (ADOFF)  sion timing control                                                                                                                       | 376<br>377<br>380<br>381                      |

|    | 19.3                 | 19.1.2<br>19.1.3<br>19.1.4<br>19.1.5<br>Conver<br>A/D cor<br>Calibra                                                     | Auto scan conversion modes  Wait for ADDAT read mode  Channel injection mode  ADC power off (ADOFF)  sion timing control  nverter interrupt control  tion                                                                                      | 376<br>377<br>380<br>381<br>382               |

|    | 19.3<br>19.4         | 19.1.2<br>19.1.3<br>19.1.4<br>19.1.5<br>Conver<br>A/D cor<br>Calibra                                                     | Auto scan conversion modes  Wait for ADDAT read mode  Channel injection mode  ADC power off (ADOFF)  sion timing control  nverter interrupt control                                                                                            | 376<br>377<br>380<br>381<br>382<br>383        |

|    | 19.3<br>19.4         | 19.1.2<br>19.1.3<br>19.1.4<br>19.1.5<br>Conver<br>A/D cor<br>Calibrate<br>A/D cor                                        | Auto scan conversion modes  Wait for ADDAT read mode  Channel injection mode  ADC power off (ADOFF)  sion timing control  nverter interrupt control  tion  nversion accuracy                                                                   | 376<br>377<br>380<br>381<br>382<br>383        |

|    | 19.3<br>19.4         | 19.1.2<br>19.1.3<br>19.1.4<br>19.1.5<br>Conver<br>A/D cor<br>Calibra<br>A/D cor<br>19.5.1                                | Auto scan conversion modes  Wait for ADDAT read mode  Channel injection mode  ADC power off (ADOFF)  sion timing control  nverter interrupt control  tion  nversion accuracy  Total unadjusted error                                           | 376<br>377<br>380<br>381<br>383<br>383        |

|    | 19.3<br>19.4         | 19.1.2<br>19.1.3<br>19.1.4<br>19.1.5<br>Conver<br>A/D cor<br>Calibrat<br>A/D cor<br>19.5.1<br>19.5.2                     | Auto scan conversion modes  Wait for ADDAT read mode  Channel injection mode  ADC power off (ADOFF)  sion timing control  nverter interrupt control  tion  nversion accuracy  Total unadjusted error  Analog reference pins                    | 376<br>377<br>380<br>381<br>382<br>383<br>385 |

| 20 | 19.3<br>19.4<br>19.5 | 19.1.2<br>19.1.3<br>19.1.4<br>19.1.5<br>Conver<br>A/D cor<br>Calibrat<br>A/D cor<br>19.5.1<br>19.5.2<br>19.5.3<br>19.5.4 | Auto scan conversion modes  Wait for ADDAT read mode  Channel injection mode  ADC power off (ADOFF)  sion timing control  nverter interrupt control  tion  nversion accuracy  Total unadjusted error  Analog reference pins  Analog input pins | 376377387381382383385385                      |

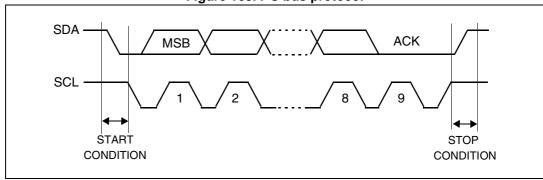

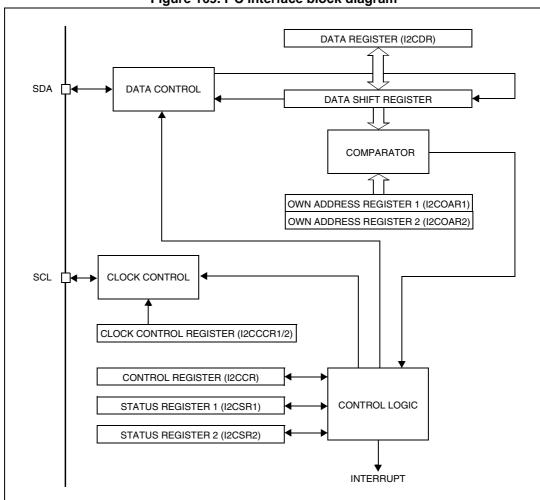

|    | 20.2 | Genera   | al description                      | 393 |

|----|------|----------|-------------------------------------|-----|

|    |      | 20.2.1   | Mode selection                      | 393 |

|    |      | 20.2.2   | Communication flow                  | 393 |

|    |      | 20.2.3   | SDA/SCL line control                | 394 |

|    | 20.3 | Functio  | onal description                    | 395 |

|    |      | 20.3.1   | Slave mode                          | 395 |

|    |      | 20.3.2   | Master mode                         | 397 |

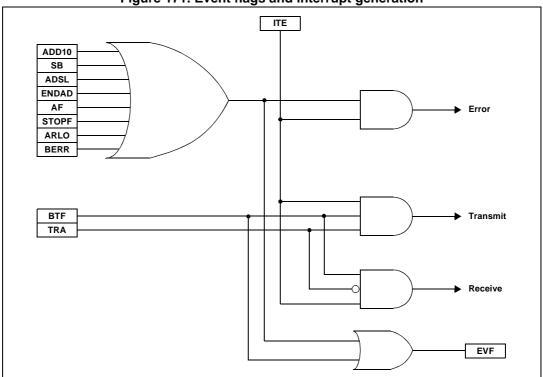

|    | 20.4 | Interrup | ots                                 | 400 |

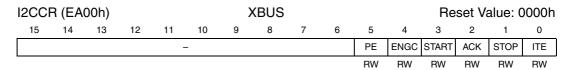

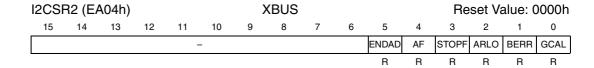

|    | 20.5 | Registe  | er description                      | 403 |

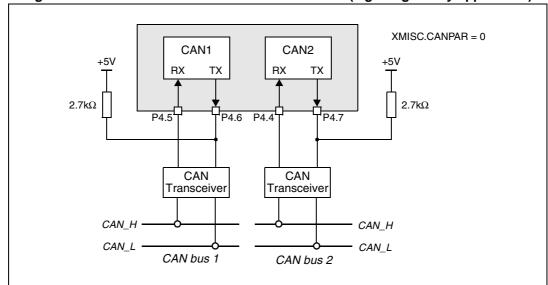

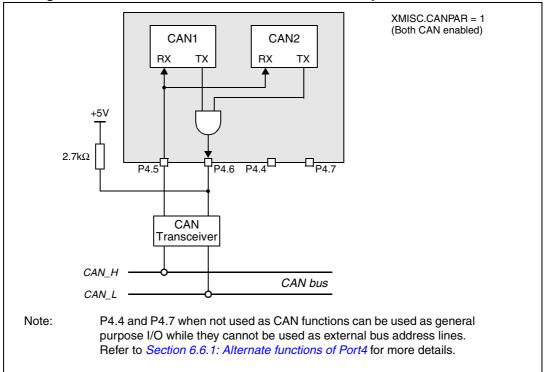

| 21 | CAN  | module   | 9S                                  | 410 |

|    | 21.1 | Memor    | y and pin mapping                   | 410 |

|    |      | 21.1.1   | CAN1 mapping                        | 410 |

|    |      | 21.1.2   | CAN2 mapping                        | 410 |

|    |      | 21.1.3   | Register summary                    | 410 |

|    | 21.2 | Interrup | ot                                  | 413 |

|    | 21.3 | Configu  | uration support                     | 413 |

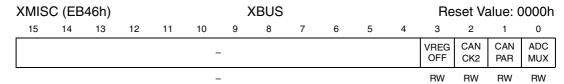

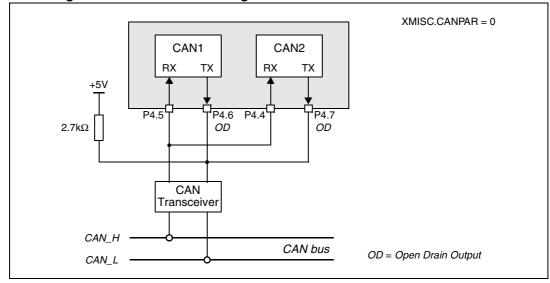

|    |      | 21.3.1   | Configuration examples              | 414 |

|    | 21.4 | Clock F  | Prescaling                          | 416 |

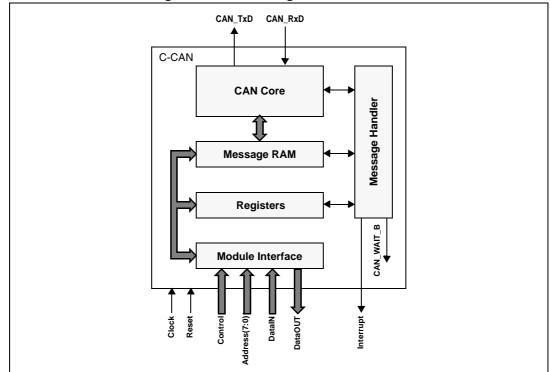

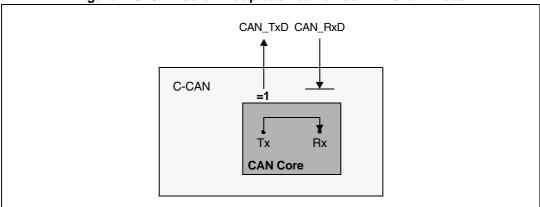

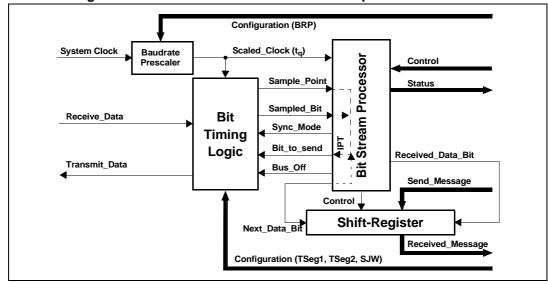

|    | 21.5 | CAN m    | odule: functional overview          | 417 |

|    | 21.6 | Block d  | diagram                             | 418 |

|    | 21.7 | Operati  | ing modes                           | 418 |

|    |      | 21.7.1   | Software initialization             | 418 |

|    |      | 21.7.2   | CAN message transfer                | 419 |

|    |      | 21.7.3   | Disabled automatic re-transmission  | 419 |

|    |      | 21.7.4   | Test mode                           | 420 |

|    |      | 21.7.5   | Silent mode                         | 420 |

|    |      | 21.7.6   | Loop back mode                      | 420 |

|    |      | 21.7.7   | Loop back combined with silent mode | 421 |

|    |      | 21.7.8   | Basic mode                          | 422 |

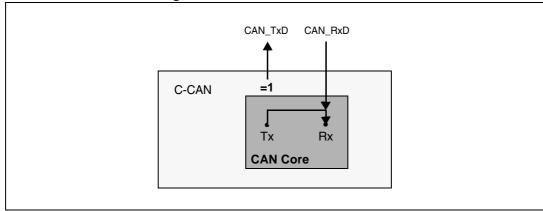

|    |      | 21.7.9   | Software control of pin CAN_TxD     | 422 |

|    | 21.8 | Prograi  | mmer's model                        | 422 |

|    |      | 21.8.1   | Hardware reset description          | 424 |

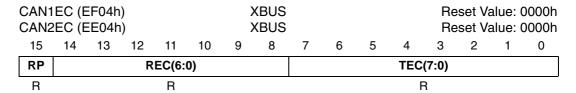

|    |      | 21.8.2   | CAN protocol related registers      |     |

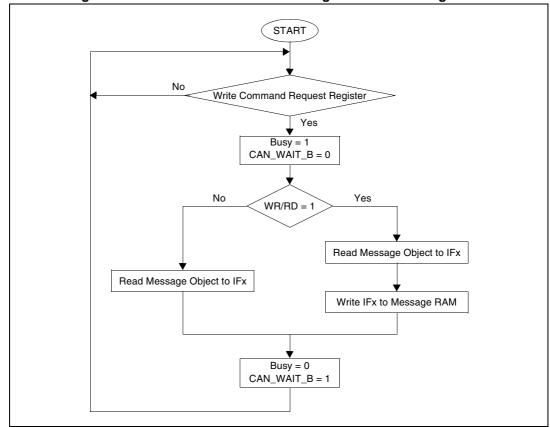

|    |      | 21.8.3   | Message interface register sets     |     |

|    |      | 21.8.4   | Message handler registers           | 441 |

|    |      |          |                                     |     |

Contents UM0404

|    | 21.9  | CAN ap    | plication                                       | 444 |

|----|-------|-----------|-------------------------------------------------|-----|

|    |       | 21.9.1    | Management of message objects                   | 444 |

|    |       | 21.9.2    | Message handler state machine                   | 445 |

|    |       | 21.9.3    | Configuration of a transmit object              | 448 |

|    |       | 21.9.4    | Updating a transmit object                      | 448 |

|    |       | 21.9.5    | Configuration of a receive object               | 448 |

|    |       | 21.9.6    | Handling of received messages                   | 449 |

|    |       | 21.9.7    | Configuration of a FIFO buffer                  | 449 |

|    |       | 21.9.8    | Reception of messages with FIFO buffers         | 450 |

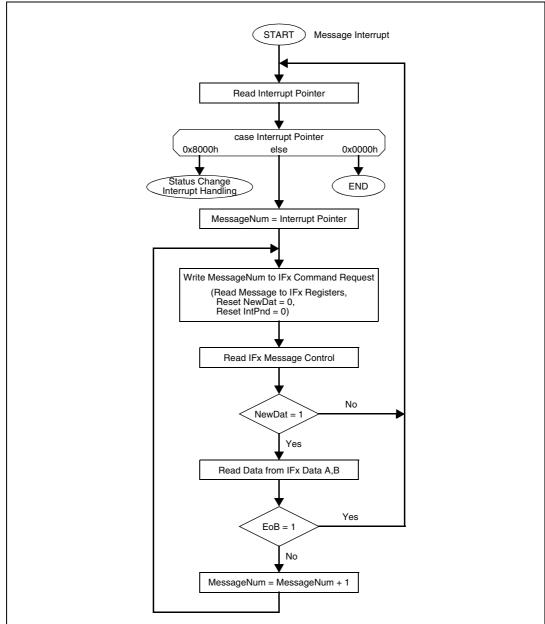

|    |       | 21.9.9    | Handling of interrupts                          |     |

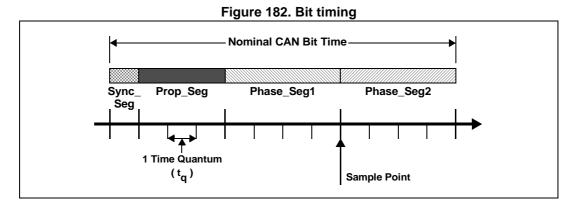

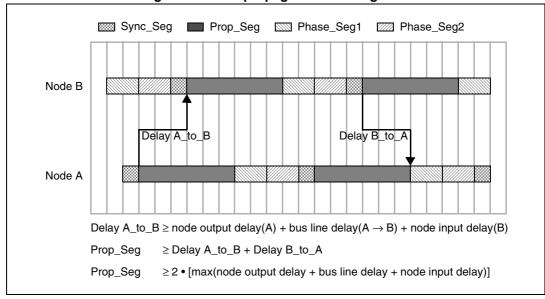

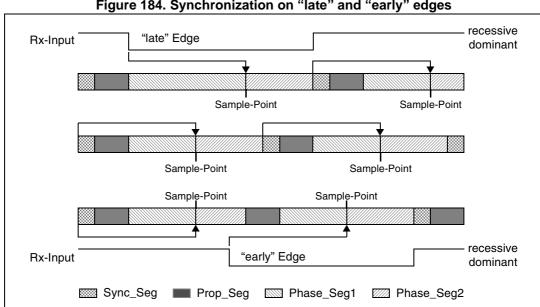

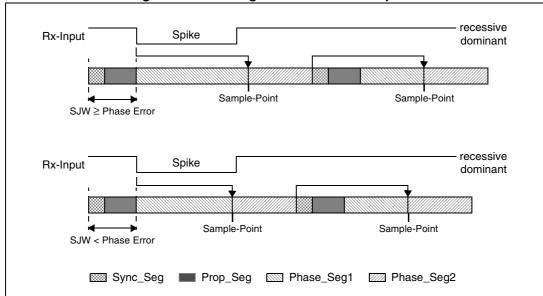

|    |       | 21.9.10   | Configuration of the bit timing                 | 452 |

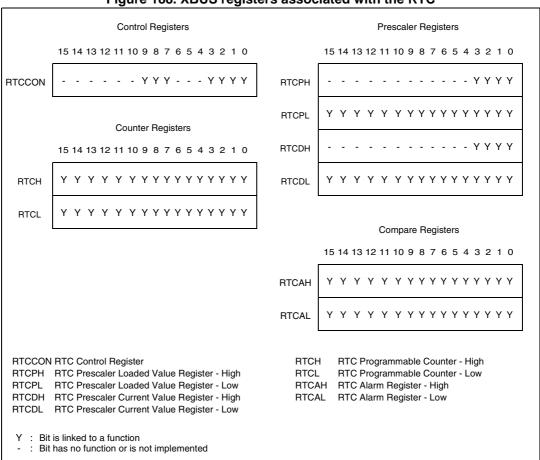

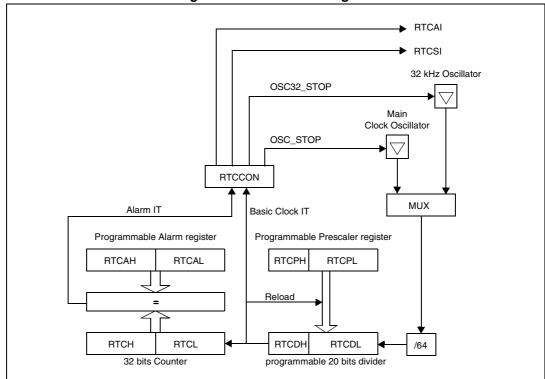

| 22 | Real  | time clo  | ck                                              | 464 |

|    | 22.1  | RTC reg   | gisters                                         | 466 |

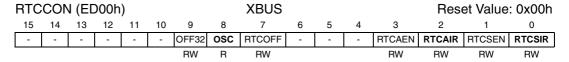

|    |       | 22.1.1    | RTCCON: RTC control register                    | 466 |

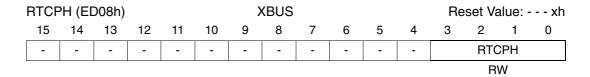

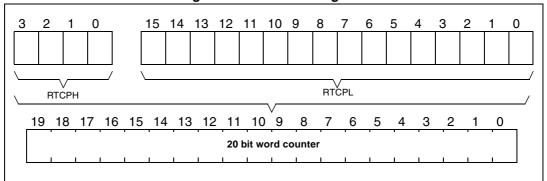

|    |       | 22.1.2    | RTCPH & RTCPL: RTC prescaler registers          | 467 |

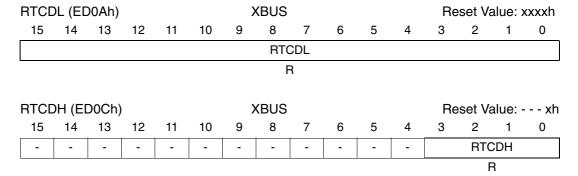

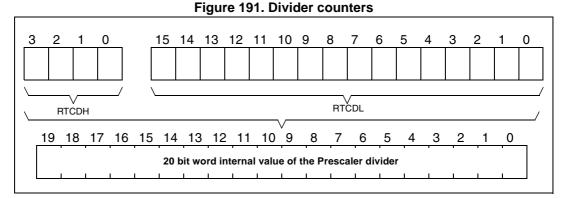

|    |       | 22.1.3    | RTCDH & RTCDL: RTC divider counters             | 468 |

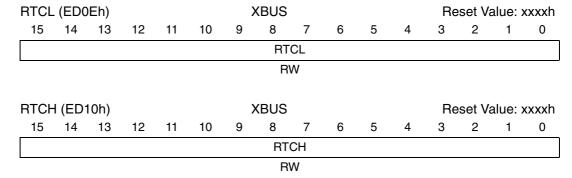

|    |       | 22.1.4    | RTCH & RTCL: RTC programmable counter registers | 469 |

|    |       | 22.1.5    | RTCAH & RTCAL: RTC alarm registers              | 469 |

|    | 22.2  | Progran   | nming the RTC                                   | 470 |

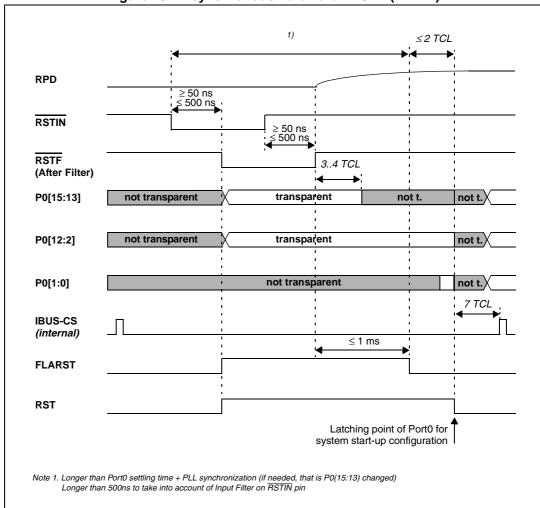

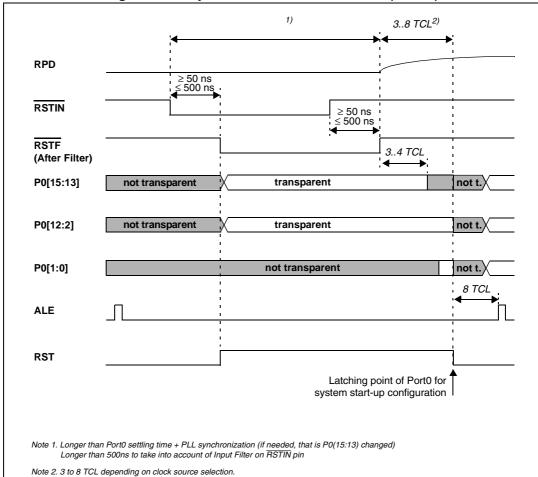

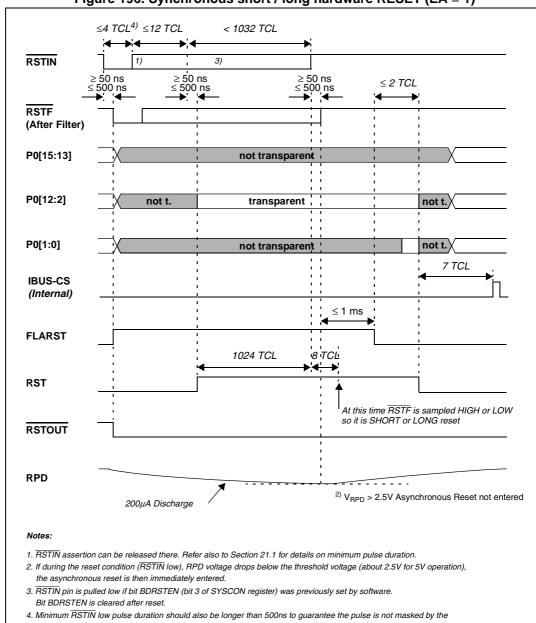

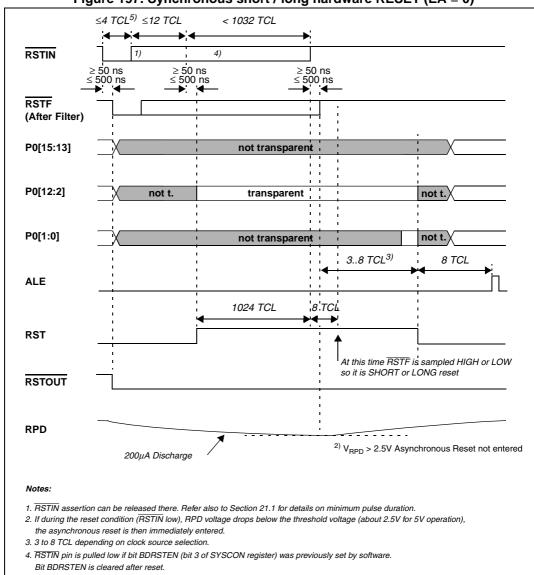

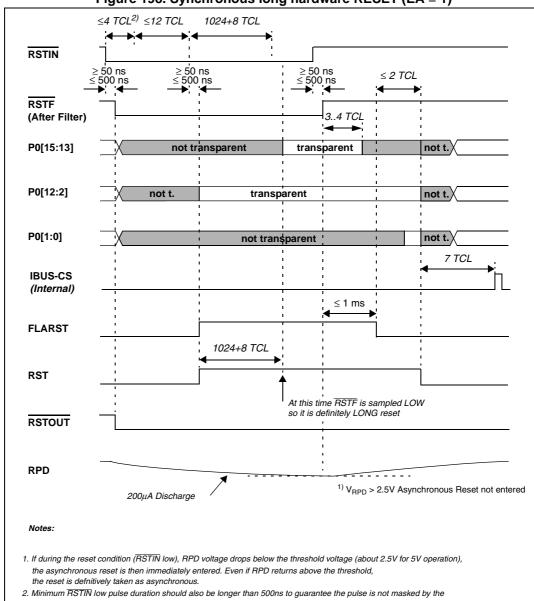

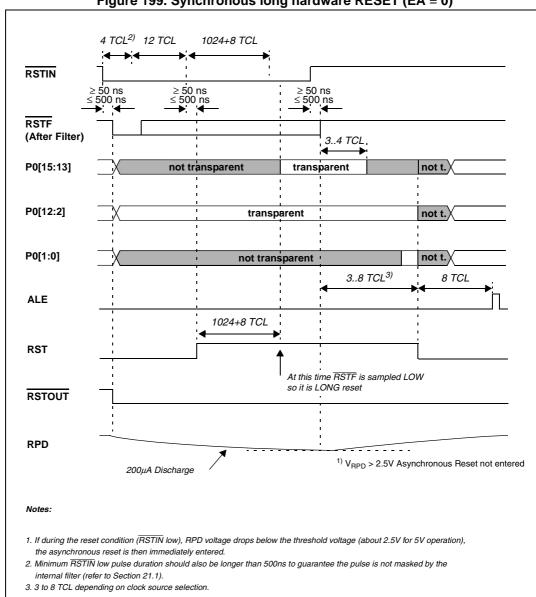

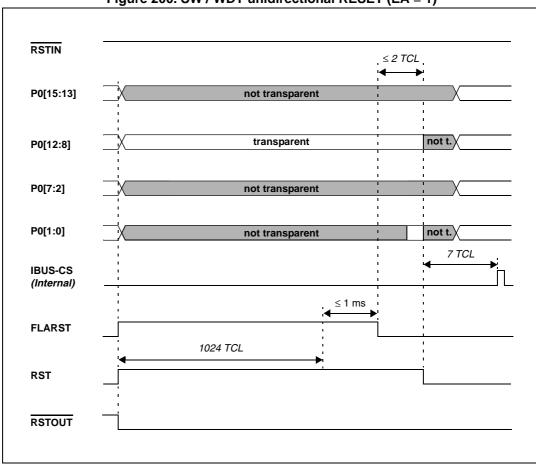

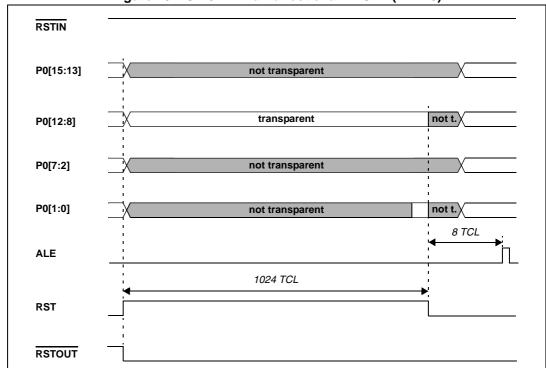

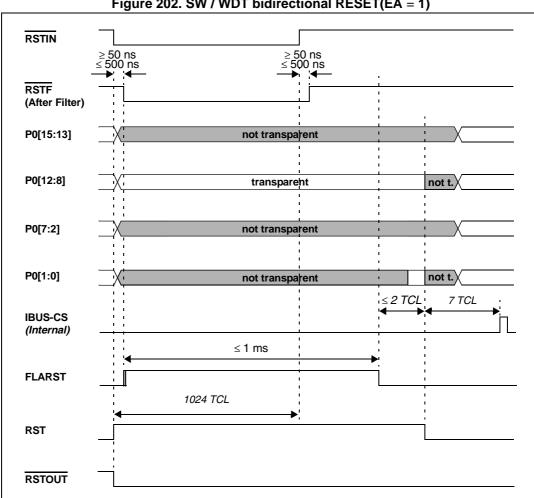

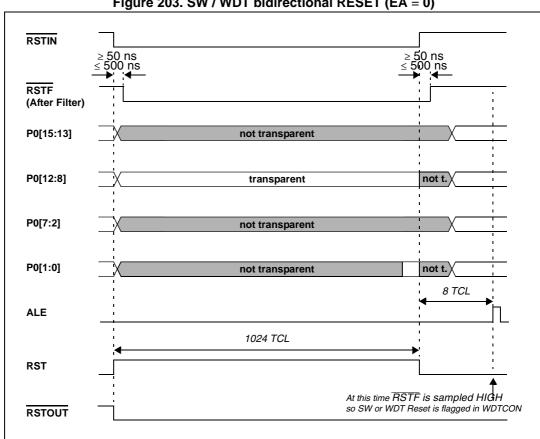

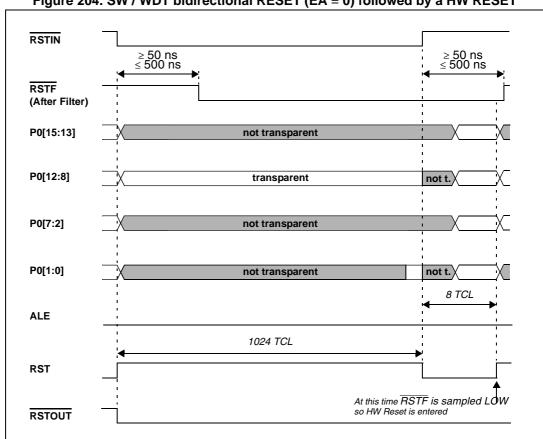

| 23 | Syste | em reset  |                                                 | 472 |

|    | 23.1  |           | er                                              |     |

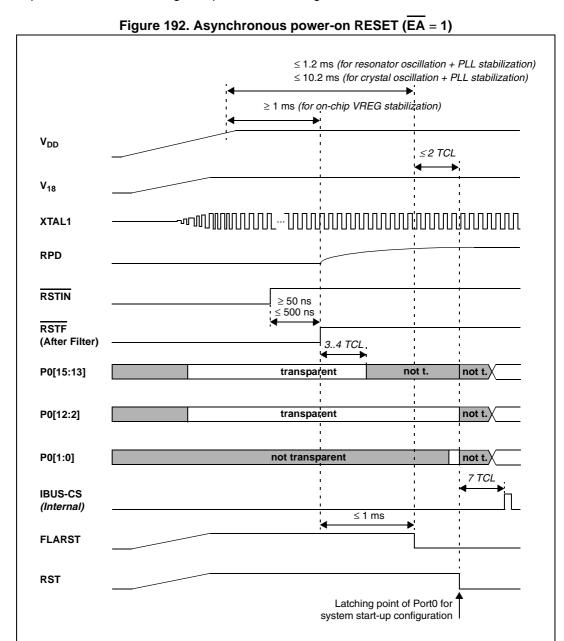

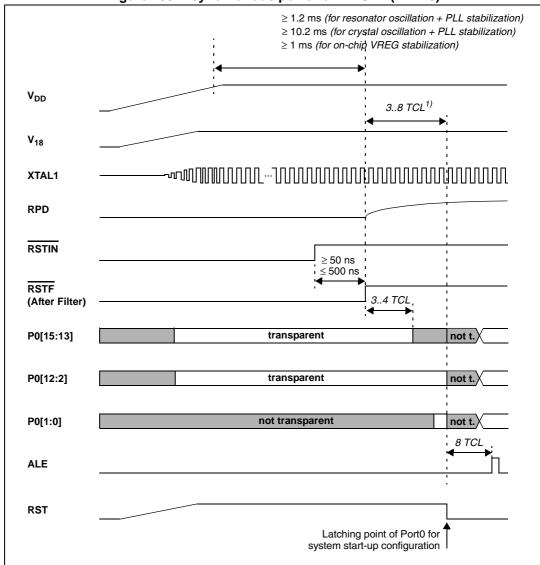

|    | 23.2  | •         | ronous reset                                    |     |

|    | 23.3  | •         | onous reset (warm reset)                        |     |

|    | 23.4  | Software  | ,                                               |     |

|    | 23.5  |           | og timer reset                                  |     |

|    |       |           |                                                 |     |

|    | 23.6  |           | onal reset                                      |     |

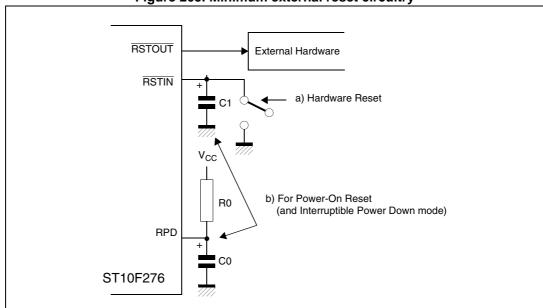

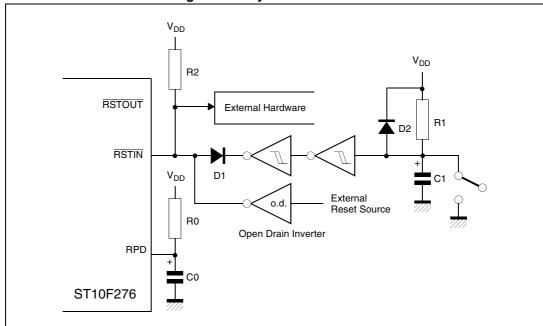

|    | 23.7  |           | ircuitry                                        |     |

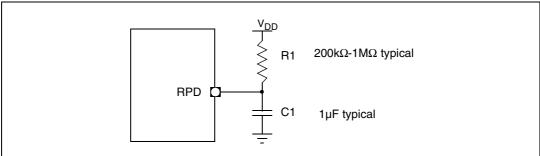

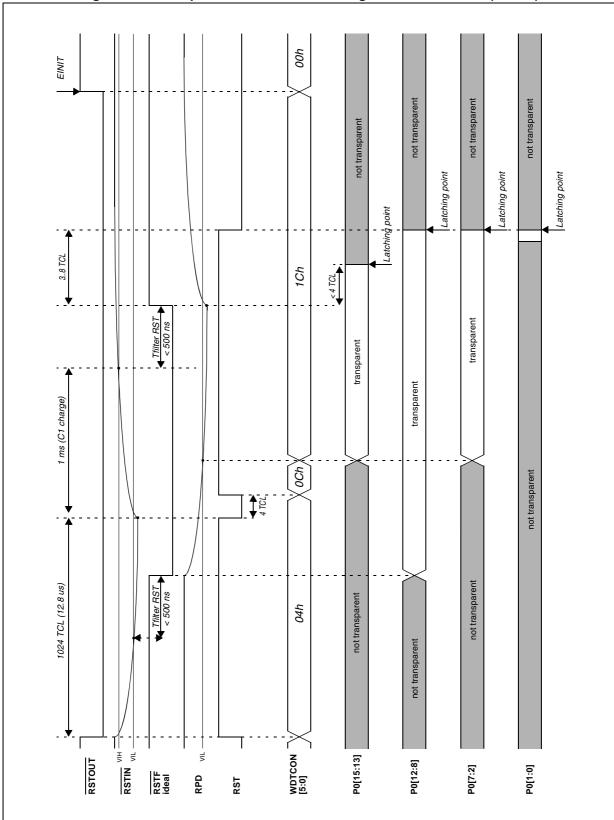

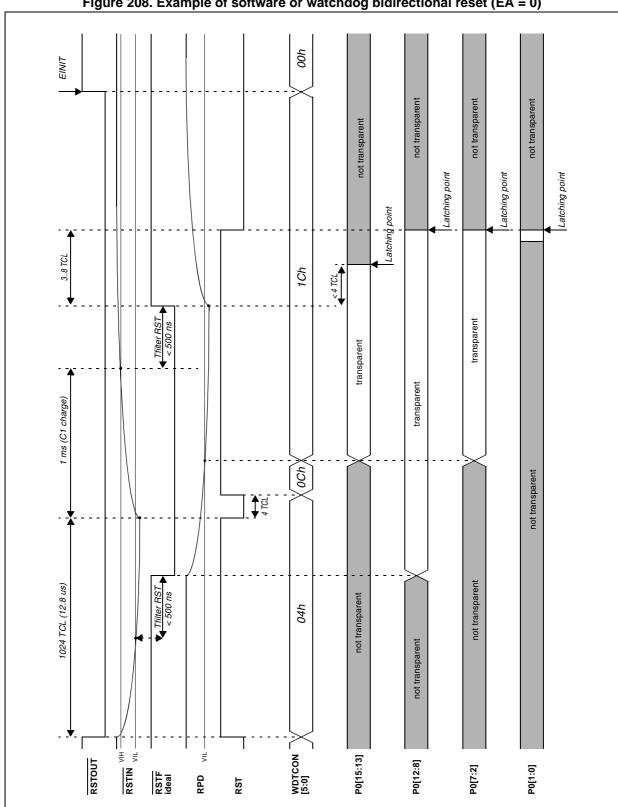

|    | 23.8  |           | pplication examples                             |     |

|    | 23.9  | Reset s   | ummary                                          |     |

|    |       | 23.9.1    | System start-up configuration                   | 496 |

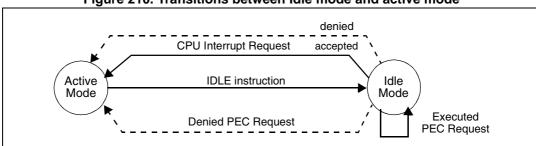

| 24 | Powe  | er reduct | tion modes                                      | 502 |

|    | 24.1  | Idle mod  | de                                              | 503 |

|    | 24.2  | Power c   | lown mode                                       | 504 |

|    |       |           |                                                 |     |

|    |       | 24.2.1    | Protected power down mode             |       |

|----|-------|-----------|---------------------------------------|-------|

|    |       | 24.2.2    | Interruptible power down mode         |       |

|    | 24.3  |           | y mode                                |       |

|    |       | 24.3.1    | Entering stand-by mode                |       |

|    |       | 24.3.2    | Exiting stand-by mode                 |       |

|    | 24.4  | 24.3.3    | Real time clock and stand-by mode     |       |

|    | 24.4  | Output    | Jiri status                           | 511   |

| 25 | Progr | ammab     | le output clock divider               | . 514 |

| 26 | Regis | ter set   |                                       | . 515 |

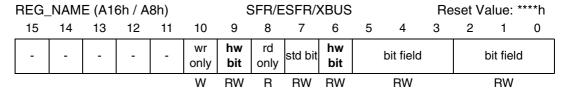

|    | 26.1  | Registe   | r description format                  | . 515 |

|    | 26.2  | General   | I purpose registers (GPRs)            | . 516 |

|    | 26.3  | Special   | function registers ordered by name    | . 517 |

|    | 26.4  | Special   | function registers ordered by address | . 524 |

|    | 26.5  | X-Regis   | sters ordered by name                 | . 531 |

|    | 26.6  | X-Regis   | sters ordered by address              | . 536 |

|    | 26.7  | Flash re  | egisters ordered by name              | . 541 |

|    | 26.8  | Flash re  | egisters ordered by address           | . 541 |

|    | 26.9  | Special   | notes                                 | . 542 |

|    | 26.10 | Identific | ation registers                       | . 543 |

| 27 | Syste | m prog    | ramming                               | . 545 |

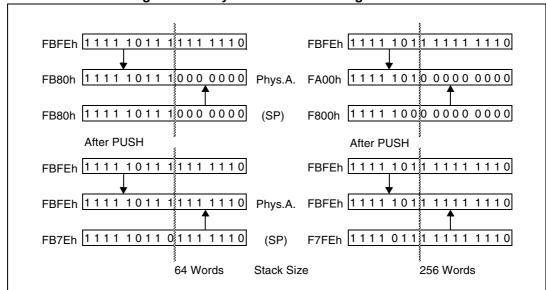

|    | 27.1  | Stack of  | perations                             | . 547 |

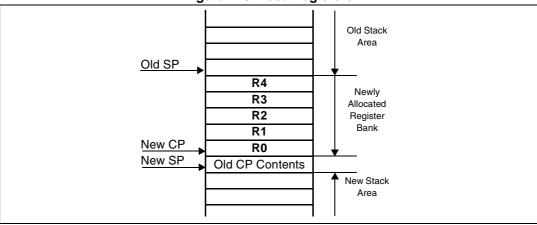

|    | 27.2  | Registe   | r banking                             | . 551 |

|    | 27.3  | Procedu   | ure call entry and exit               | . 551 |

|    | 27.4  | Table se  | earching                              | . 553 |

|    | 27.5  | Periphe   | ral control and interface             | . 554 |

|    | 27.6  | Floating  | point support                         | . 554 |

|    | 27.7  | Trap / in | nterrupt entry and exit               | . 554 |

|    | 27.8  | Insepara  | able instruction sequences            | . 555 |

|    | 27.9  | Overridi  | ing the DPP addressing mechanism      | . 555 |

|    | 27.10 | Handlin   | g the internal Flash                  | . 556 |

|    | 27.11 | Pits, tra | ps and mines                          | . 558 |

|    |       |           |                                       |       |

| Contents     | UM                  | 0404 |

|--------------|---------------------|------|

| Appendix A   | Abbreviations       | 559  |

| Appendix B   | Document references | 560  |

| Revision his | tory                | 561  |

UM0404 List of tables

# List of tables

| Table 1.  | Protected bit                                                        |     |

|-----------|----------------------------------------------------------------------|-----|

| Table 2.  | Segment 8 address range mapping                                      | 43  |

| Table 3.  | 512 Kbyte IFlash memory block organization                           |     |

| Table 4.  | 320 Kbyte XFlash memory block organization                           | 43  |

| Table 5.  | Stack size                                                           | 46  |

| Table 6.  | Mapping of general purpose registers to RAM addresses                | 47  |

| Table 7.  | Minimum execution times                                              | 61  |

| Table 8.  | Stack size                                                           | 64  |

| Table 9.  | Shift right rounding error evaluation                                | 69  |

| Table 10. | Pointer post-modification combinations for IDXi and Rwn              | 85  |

| Table 11. | Parallel data move addressing                                        |     |

| Table 12. | Limiter output using CoSTORE instruction                             | 88  |

| Table 13. | MAC register address in CoReg addressing mode                        | 94  |

| Table 14. | MAC instruction set summary                                          | 94  |

| Table 15. | Interrupt and PEC service request sources                            | 97  |

| Table 16. | Vector locations and status for hardware traps                       | 99  |

| Table 17. | PEC control register addresses                                       | 104 |

| Table 18. | Example of software controlled interrupt classes                     | 107 |

| Table 19. | Pins to be used as external interrupt inputs                         |     |

| Table 20. | X-Interrupt detailed mapping                                         |     |

| Table 21. | Trap priorities                                                      |     |

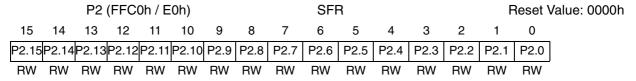

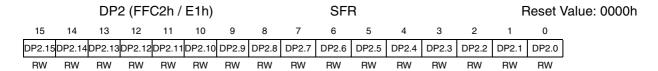

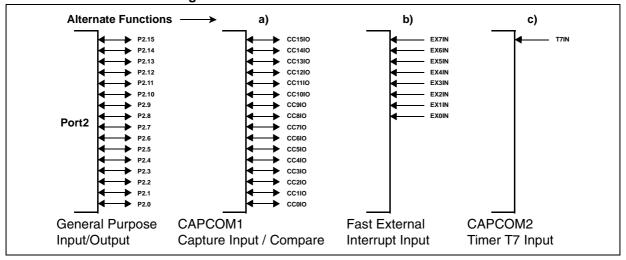

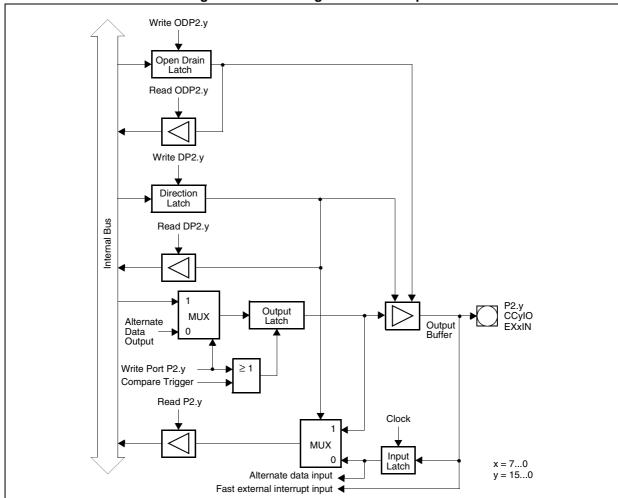

| Table 22. | Port2 alternate functions                                            |     |

| Table 23. | Port3 alternative functions                                          |     |

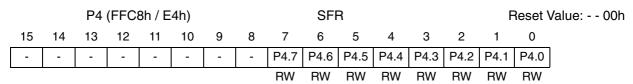

| Table 24. | Port4 alternate functions                                            |     |

| Table 25. | Port5 alternate functions                                            |     |

| Table 26. | Port6 alternate functions                                            |     |

| Table 27. | Port7 alternate functions                                            |     |

| Table 28. | Port8 alternate functions                                            |     |

| Table 29. | Summary of dedicated pins                                            |     |

| Table 30. | Definition of address areas                                          |     |

| Table 31. | Status of the external bus interface during EBC idle state           |     |

| Table 32. | Definition of XBUS address areas                                     |     |

| Table 33. | GPT1 core timer T3 count direction control                           |     |

| Table 34. | GPT1 timer resolutions                                               |     |

| Table 35. | GPT1 core timer T3 (counter mode) input edge selection               |     |

| Table 36. | GPT1 core timer T3 (incremental interface mode) input edge selection |     |

| Table 37. | GPT1 auxiliary timer (counter mode) input edge selection             |     |

| Table 38. | GPT2 core timer T6 count direction control                           |     |

| Table 39. | GPT2 timer resolution                                                |     |

| Table 40. | GPT2 core timer T6 (counter mode) input edge selection               |     |

| Table 41. | GPT2 auxiliary timer (counter mode) input edge selection             |     |

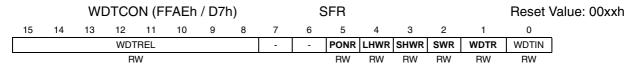

| Table 42. | WDTCON bits value on different resets                                |     |

| Table 43. | WDTREL reload value                                                  |     |

| Table 44. | Reset events summary                                                 |     |

| Table 45. | ST10F276x boot mode selection                                        |     |

| Table 46. | Ranges of timer contents versus BRP value                            |     |

| Table 47. | Software topics summary                                              |     |

| Table 48. | Hardware topics summary                                              | 320 |

List of tables UM0404

| Table 49. | Summary of compare modes                                   | . 337 |

|-----------|------------------------------------------------------------|-------|

| Table 50. | Register pairs for double-register compare mode            | . 341 |

| Table 51. | CAPCOM unit interrupt control register addresses           |       |

| Table 52. | PWM frequencies                                            | . 352 |

| Table 53. | PWM module channel specific register addresses             | . 353 |

| Table 54. | XPWM frequencies                                           | . 364 |

| Table 55. | XPWM module channel specific register addresses            | . 365 |

| Table 56. | ADC sampling and conversion timing                         | . 382 |

| Table 57. | Interrupt event summary                                    | . 401 |

| Table 58. | CAN1 register mapping                                      |       |

| Table 59. | CAN2 register mapping                                      | . 412 |

| Table 60. | C-CAN register memory space summary                        | . 423 |

| Table 61. | IF1 and IF2 message interface register sets                | . 429 |

| Table 62. | Parameters of the CAN bit time                             | . 453 |

| Table 63. | Reset event definition                                     | . 472 |

| Table 64. | Reset events summary                                       | . 495 |

| Table 65. | PORT0 latched configuration for the different reset events | . 497 |

| Table 66. | Power reduction modes summary                              | . 503 |

| Table 67. | Output pin state during Idle and power down modes          | . 512 |

| Table 68. | General purpose registers (GPRs)                           |       |

| Table 69. | General purpose registers (GPRs) bit wise addressing       | . 516 |

| Table 70. | Special function registers ordered by name                 | . 517 |

| Table 71. | Special function registers ordered by address              | . 524 |

| Table 72. | X-Registers ordered by name                                | . 531 |

| Table 73. | X-Registers ordered by address                             | . 536 |

| Table 74. | Flash registers ordered by name                            | . 541 |

| Table 75. | Flash registers ordered by address                         | . 541 |

| Table 76. | Stack size selection                                       | . 548 |

| Table 77. | Document revision history                                  | . 561 |

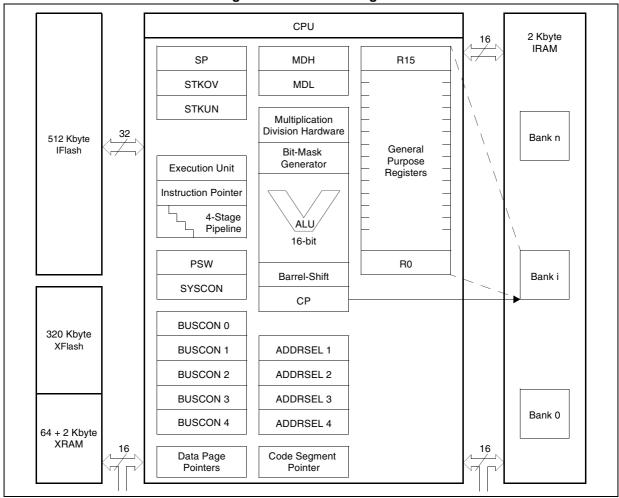

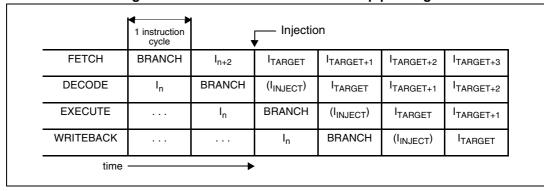

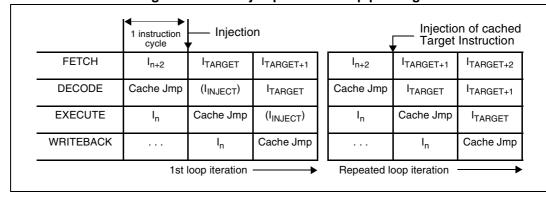

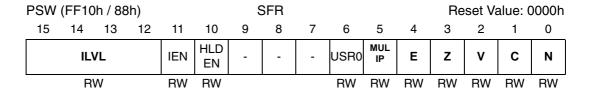

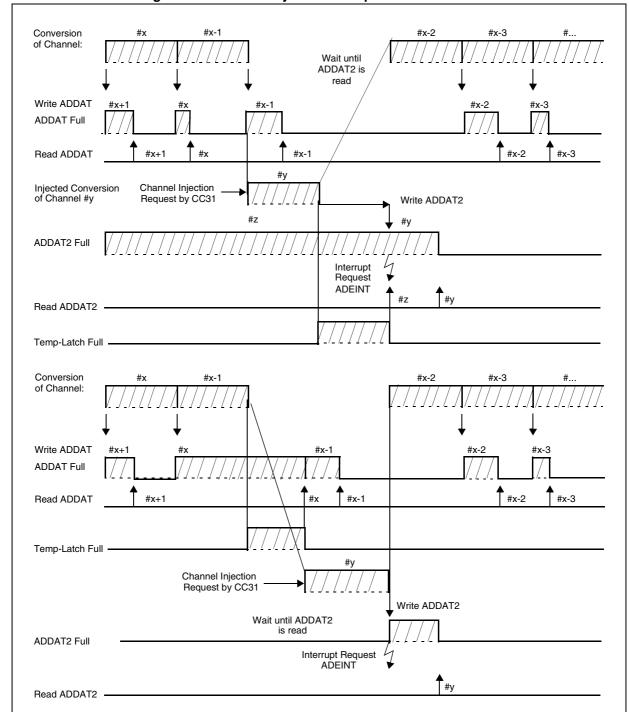

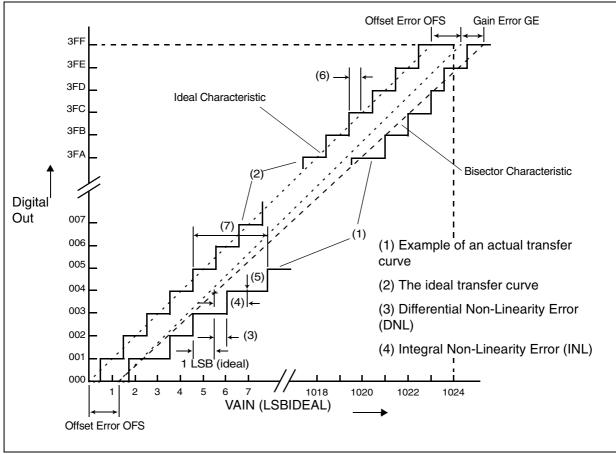

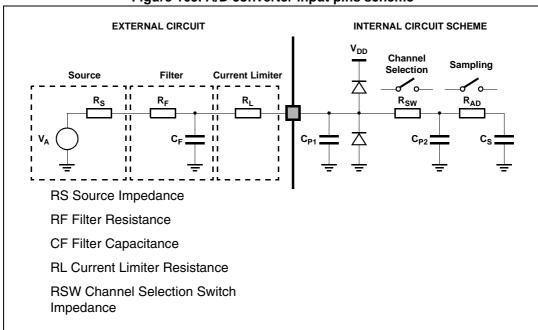

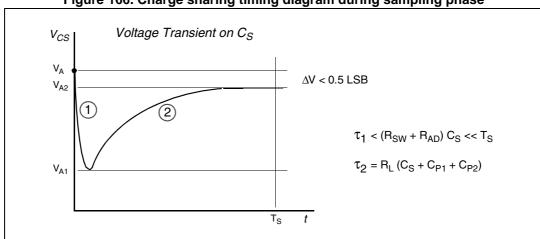

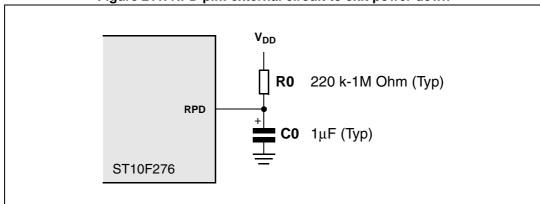

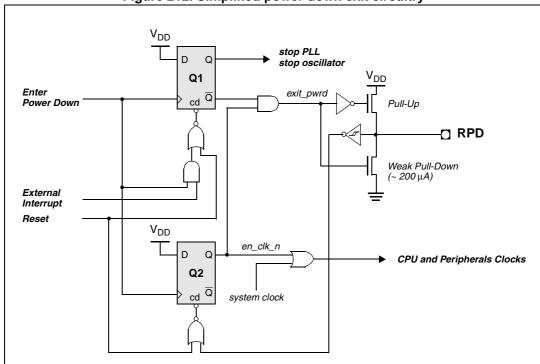

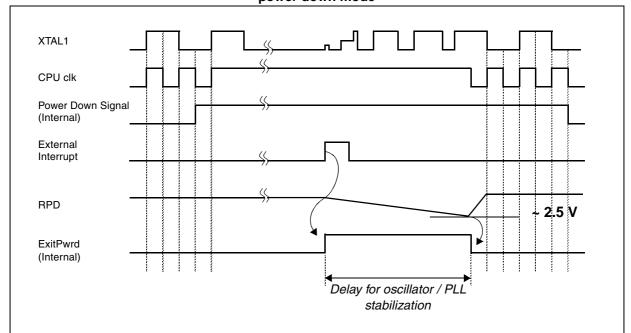

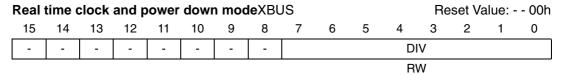

UM0404 List of figures